# JZ8P1525

8位 OTP 微控制器

用户数据手册

版本号 V1.2

#### 修改记录说明

| 版本号   | 修改说明                   | 备注 |

|-------|------------------------|----|

| V1. 0 | 完成初稿                   |    |

| V1. 1 | 修改内容格式                 |    |

| V1.2  | 修改 RPAGE\IOPAGE 寄存器区表格 |    |

#### 声明:

- 本资料内容,随产品的改进,会进行相应更新,恕不另行通知。使用本资料前请咨询我司销售人员,以保证本资料内容为最新版本。

- 请在本资料所记载的极限范围内使用本产品,因使用不当造成的损失,我司不承担其责任。

- 尽管本公司一向致力于提高产品质量与可靠性,但是半导体产品本身有一定的概率发生故障或错误工作,为防止因此类事故而造成的人身伤害或财产损失,请在使用过程中充分留心安全设计。

- 将本产品或者本资料出口海外时,应当遵守适用的进出口管制法律法规。

- 未经本公司许可,严禁以任何形式复制或转载本资料的部分或全部内容。

- 本资料测试数据仅供参考,实际数据以目标样机测试为准。

# 目录

| 1 | 芯片简介                                      | 6  |

|---|-------------------------------------------|----|

|   | 1.1 功能特性                                  | 6  |

|   | 1.2 引脚分配                                  | 7  |

|   | 1.3 引脚说明                                  | 8  |

|   | 1.4 系统框图                                  | 9  |

| 2 | 存储器结构                                     | 10 |

|   | 2.1程序存储器区                                 | 10 |

|   | 2.2 数据存储器区                                | 11 |

|   | RPAGE\IOPAGE 寄存器区(IOPAGE 只能使用 IR/IW 指令读写) | 11 |

| 3 | 功能模块                                      | 12 |

|   | 3.1 操作寄存器                                 | 12 |

|   | 3.1.1 RPAGE~RO-IAR(间接地址存储器)               | 12 |

|   | 3.1.2 RPAGE~R1-TCC(TCC 定时计数器)             | 12 |

|   | 3.1.3 RPAGE~R2-PCL(PC 程序计数器)              | 12 |

|   | 3.1.4 RPAGE~R3-STATUS(STATUS 状态寄存器)       | 13 |

|   | 3.1.5 RPAGE~R4-RSR(FSR RAM 选择寄存器)         | 14 |

|   | 3.1.6 RPAGE~R6-PORT6(PORT6 数据寄存器)         |    |

|   | 3.1.7 RPAGE~R8-PWMCON(PWM 控制寄存器)          | 14 |

|   | 3.1.8 RPAGE~R9-PRD(PWM 周期寄存器)             |    |

|   | 3.1.9 RPAGE~RA-PDC1(PWM1 占空比寄存器)          |    |

|   | 3.1.10 RPAGE~RB-PDC2(PWM2 占空比寄存器)         |    |

|   | 3.1.11 RPAGE~RC-PDC3(PWM3 占空比寄存器)         |    |

|   | 3. 1. 12 RPAGE~RD-ICIECR (P6 端口中断唤醒使能寄存器) |    |

|   | 3.1.13 RPAGE~RE-CPUCON(CPU 模式控制寄存器)       |    |

|   | 3.1.14 RPAGE~RF-ISR(中断标志寄存器)              |    |

|   | 3.2 控制寄存器                                 |    |

|   | 3.2.1 CONT (控制寄存器)                        | _  |

|   | 3.2.2 IOPAGE~IOC6-P6CR (P6 方向控制寄存器)       |    |

|   | 3.2.3 IOPAGE~IOC7-HDSOCR(驱动增强控制寄存器 0)     |    |

|   | 3. 2. 4 IOPAGE~IOC8-HDS1CR(驱动增强控制寄存器 1)   |    |

|   | 3.2.5 IOPAGE~IOC9-PHDCR(端口上下拉控制寄存器)       |    |

|   | 3.2.6 IOPAGE~IOCA-HDS2CR(驱动增强控制寄存器 2)     |    |

|   | 3.2.7 IOPAGE~IOCB-PDCR(端口下拉控制寄存器)         |    |

|   | 3.2.8 IOPAGE~IOCC-ODCR (P6 开漏控制寄存器)       |    |

|   | 3.2.9 IOPAGE~IOCD-PHCR (P6 端口上拉控制寄存器)     |    |

|   | 3.2.10 IOPAGE~IOCE-WDTCR(看门狗控制寄存器)        |    |

|   | 3.2.11 IOPAGF~IOCF-IMR(中断使能控制寄存器)         |    |

|   | 3. 3 GPIO 功能模块<br>3. 3. 1 GPIO 寄存器说明      |    |

|   |                                           |    |

|   | RPAGE~R6-PORT6 (PORT6 数据寄存器)              |    |

|   | IOPAGE~10C6-P6CR (P6 方向控制奇存器)             |    |

|   | 10PAGE~10C7-HDS0CR(驱动增强控制寄存器 0)           |    |

|   | TUPAGE~1008-IIDS1CR(驱列增独控制句仔裔 1)          | 23 |

|      | IOPAGE~IOC9-PHDCR(端口上下拉控制寄存器)                         | 26 |

|------|-------------------------------------------------------|----|

|      | IOPAGE~IOCA-HDS2CR(驱动增强控制寄存器 2)                       | 26 |

|      | IOPAGE~IOCB-PDCR(端口下拉控制寄存器)                           | 26 |

|      | IOPAGE~IOCC-ODCR(P6 开漏控制寄存器)                          | 27 |

|      | IOPAGE~IOCD-PHCR(P6端口上拉控制寄存器)                         | 27 |

| 3.4  | TCC 定时器功能模块                                           | 28 |

|      | 3. 4. 1 TCC 定时器寄存器说明                                  | 28 |

|      | CONT (控制寄存器)                                          | 28 |

|      | 注意:CONT 寄存器 Bit. 2~0(PSR2~PSR0)分频选择位在切换状态时,需先关闭看门狗使能, | 待切 |

|      | 换完成后再打开看门狗使能,否则容易导致复位。                                | 29 |

|      | RPAGE~R1-TCC(TCC 定时计数器)                               | 29 |

|      | RPAGE~RE-CPUCON(CPU 模式控制寄存器)                          | 29 |

|      | RPAGE~RF-ISR(中断标志寄存器)                                 | 30 |

|      | IOPAGF~IOCF-IMR(WDT唤醒及中断使能控制寄存器)                      | 30 |

|      | 3. 4. 2 TCC 定时设置说明                                    | 30 |

|      | 3. 4. 3 TCC 定时计算说明                                    | 30 |

| 3. 5 | 工作模式                                                  | 31 |

|      | 3. 5. 1 高速模式                                          | 31 |

|      | 3. 5. 2 低速模式                                          | 32 |

|      | 3. 5. 3 空闲模式                                          | 32 |

|      | 3. 5. 4 睡眠模式                                          | 33 |

| 3.6  | 睡眠唤醒功能模块                                              | 34 |

|      | 3. 6. 1 睡眠唤醒方式说明                                      | 34 |

|      | 3.6.2 相关寄存器说明                                         | 34 |

|      | CONT (控制寄存器)                                          | 34 |

|      | RPAGE~RD-ICIECR(P6端口中断唤醒使能寄存器)                        | 34 |

|      | RPAGE~RE-CPUCON(CPU 模式控制寄存器)                          | 34 |

|      | RPAGE~RF-ISR(中断标志寄存器)                                 |    |

|      | IOPAGE~IOCE-WDTCR(看门狗控制寄存器)                           | 35 |

|      | IOPAGF~IOCF-IMR(WDT唤醒及中断使能控制寄存器)                      | 36 |

|      | 3.6.3 端口状态改变查询方式唤醒设置                                  | 36 |

|      | 3.6.4 端口状态改变中断方式唤醒设置                                  |    |

|      | 3. 6. 5 重要说明                                          | 36 |

| 3. 7 | PWM 脉宽调制功能模块                                          |    |

|      | 3.7.1 PWM 脉宽调制寄存器说明                                   | 38 |

|      | RPAGE~R8-PWMCON(PWM 控制寄存器)                            | 38 |

|      | RPAGE~R9-PRD(PWM 周期寄存器)                               |    |

|      | RPAGE~RA-PDC1(PWM1 占空比寄存器)                            |    |

|      | RPAGE~RB-PDC2(PWM2 占空比寄存器)                            | 39 |

|      | RPAGE~RC-PDC3(PWM3 占空比寄存器)                            |    |

|      | RPAGE~RE-CPUCON(CPU 模式控制寄存器)                          |    |

|      | RPAGE~RF-ISR(中断标志寄存器)                                 |    |

|      | IOPAGE~IOCE-WDTCR(看门狗控制寄存器)                           |    |

|      | IOPAGF~IOCF-IMR(WDT唤醒及中断使能控制寄存器)                      |    |

|      | 3.7.2 PWM 脉宽调制设置说明                                    | 40 |

|   | 3.7.3 PWM 计算说明          | 40     |

|---|-------------------------|--------|

|   | 3.8 中断功能模块              | 42     |

|   | 3.8.1 中断寄存器说明           | 42     |

|   | RPAGE~RF-ISR(中断标志寄存器)   | 42     |

|   | IOPAGF~IOCF-IMR(中断使能控制  | 寄存器)42 |

|   | 3.9 复位功能模块              | 44     |

|   | 3.9.1 WDT 看门狗复位         | 44     |

|   | 3.9.2 POR 上电复位          | 44     |

|   | 3.9.3 LVR 低电压复位         | 45     |

|   | 3.9.4 工作频率与 LVR 低压检测关系  | 46     |

|   | 3.9.5 寄存器上电复位值          | 46     |

|   | 3.10 系统时钟功能模块           | 48     |

|   | 3.10.1 内部 RC 振荡器模式(IRC) | 48     |

|   | 3.10.2 外部晶体振荡器/陶瓷谐振器    | (XT)48 |

|   | 3.10.3 时钟模块应用说明         | 49     |

| 4 | 4 CODE OPTION 寄存器       | 50     |

| 5 | 5 芯片电气特性                | 52     |

|   | 5.1 芯片极限参数              | 52     |

|   | 5.2 芯片直流参数              | 52     |

| 6 | 6 封装尺寸信息                | 53     |

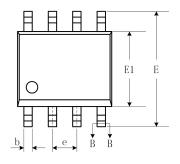

|   | 6.1 8PIN 封装尺寸           | 53     |

|   | 6 2 6PIN 封装尺寸           | 54     |

# 1 芯片简介

# 1.1 功能特性

#### CPU 配置

- 1K×14-Bit OTP ROM

- 48×8-Bit SRAM

- 5级堆栈空间

- 工作电流小于 1.1 mA (8MHz/5V)

- 工作电流 20 μA (32KHz/3V)

- 休眠电流小于1 μA (休眠模式)

#### I/0 配置

- 1组双向 IO 端口:P6

- P63 可配置上下拉和输出

- 唤醒端口:P6 口

- 6个可编程上拉 I/0 引脚

- 6个可编程下拉 I/0 引脚

- 6个可编程开漏输出引脚

- 端口驱动增强 6 级可选: P60, P61, P62

- 端口可配置弱驱动: P63, P64, P65

- 外部中断:P60

# 工作电压

工作电压范围:

1.8V~5.5V (0℃-70℃)

2.3V~5.5V (-40℃-85℃)

常温(25℃)工作电压可低至1.5V

# 工作频率范围

- 外部晶振 HXT, LXT

- 外部晶振内置电容: Disable、14Pf、18Pf、25Pf

- 内部 IHRC 选择: 910KHz/1MHz/8MHz

- 内部 ILRC 选择: 14KHz (5V) /8KHz (3V)

● 时钟周期分频选择: 2Clock, 4Clock, 8Clock, 16Clock, 32Clock

# 低压复位

- 1.  $2V \pm 0$ . 3V, 1.  $6V \pm 0$ . 3V

- 1.8 $V \pm 0$ .3V、2.3 $V \pm 0$ .2V

- 2.5 $V \pm 0.2V$ , 2.9 $V \pm 0.2V$

- 3.  $1V \pm 0. 2V$ ,  $3. 3V \pm 0. 2V$

# 中断源

- TCC 溢出中断

- 外部中断

- 输入端口状态改变产生中断

- T1/PWM 周期溢出中断

# 外围模块

- 可编程 WDT 定时器 4.5ms、18ms、72ms、288ms

- 3路共周期8Bit PWM

- 8Bit 实时时钟/计数器

# 封装类型

- JZ8P1525-DIP8;

- JZ8P1525-S0P8;

- JZ8P1525-S0T23-6;

# 1.2 引脚分配

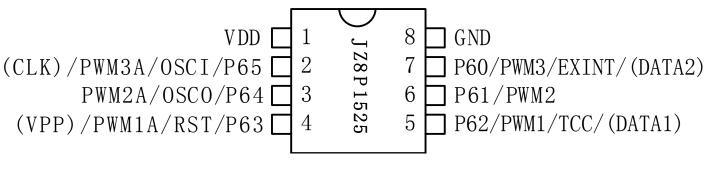

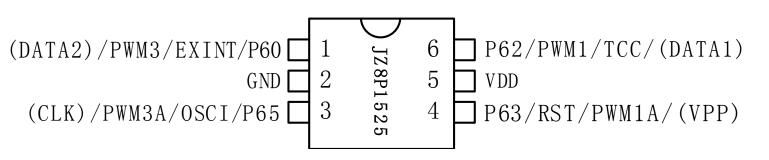

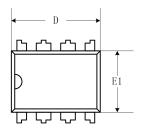

JZ8P1525-8PIN 脚位图

JZ8P1525-6PIN 脚位图

# 1.3 引脚说明

|     | 7175  | 1 00.71    |                       |  |  |  |  |  |

|-----|-------|------------|-----------------------|--|--|--|--|--|

| 序号  | 管脚名   | I/0        | 功能描述                  |  |  |  |  |  |

|     | P60   | I/0 (上/下拉) | GPIO,可编程上下拉、高驱动、端口唤醒  |  |  |  |  |  |

| DCO | EXINT | I (SMT)    | 外部中断输入端口              |  |  |  |  |  |

| P60 | PWM3  | 0          | PWM3 输出               |  |  |  |  |  |

|     | Data2 | I (SMT)    | 烧录数据口                 |  |  |  |  |  |

| DC1 | P61   | I/0 (上/下拉) | GPIO, 可编程上下拉、高驱动、端口唤醒 |  |  |  |  |  |

| P61 | PWM2  | 0          | PWM2 输出               |  |  |  |  |  |

|     | P62   | I/0 (上/下拉) | GPIO, 可编程上下拉、高驱动、端口唤醒 |  |  |  |  |  |

| DCO | TCC   | I          | 外部 TCC 信号源输入脚         |  |  |  |  |  |

| P62 | PWM1  | 0          | PWM1 输出               |  |  |  |  |  |

|     | Data1 | I (SMT)    | 烧录数据口                 |  |  |  |  |  |

|     | P63   | I/0 (上拉)   | GPIO,可编程上下拉、高驱动、端口唤醒  |  |  |  |  |  |

| DC0 | RST   | I (SMT)    | 复位脚                   |  |  |  |  |  |

| P63 | PWM1A | 0          | PWM1 映射输出口            |  |  |  |  |  |

|     | vpp   | I          | 烧录高压口                 |  |  |  |  |  |

|     | P64   | I/0 (上/下拉) | GPIO, 可编程上下拉、高驱动、端口唤醒 |  |  |  |  |  |

| P64 | OSCO  | 0          | 晶振/陶振的时钟输出端           |  |  |  |  |  |

|     | PWM2A | 0          | PWM2 映射输出口            |  |  |  |  |  |

|     | P65   | I/0 (上/下拉) | GPIO,可编程上下拉、高驱动、端口唤醒  |  |  |  |  |  |

| DGE | OSCI  | I          | 晶振/陶振的时钟输入端           |  |  |  |  |  |

| P65 | PWM3A | 0          | PWM3 映射输出口            |  |  |  |  |  |

|     | c1k   | I (SMT)    | 烧录时钟口                 |  |  |  |  |  |

|     | VDD   |            | 电源                    |  |  |  |  |  |

|     | VSS   |            | 地                     |  |  |  |  |  |

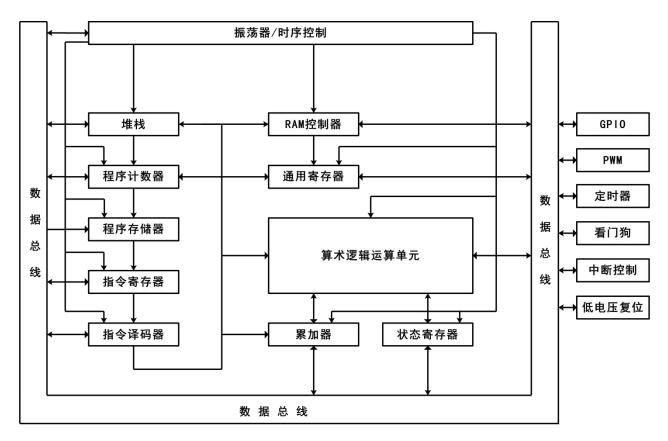

# 1.4 系统框图

系统电路框图

# 2 存储器结构

# 2.1程序存储器区

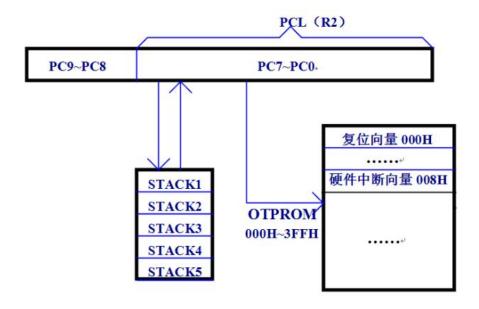

程序存储器区结构图

# 2.2 数据存储器区

# RPAGE\IOPAGE 寄存器区(IOPAGE 只能使用 IR/IW 指令读写)

| 地址                | RPAGE 页面寄存器            | IOPAGE 页面寄存器             |

|-------------------|------------------------|--------------------------|

| 0x00              | RO(间接地址存储器)            | 保留                       |

| 0x01              | R1/TCC(TCC 定时计数器)      | CONT (控制寄存器)             |

| 0x02              | R2(PC 程序计数器)           | 保留                       |

| 0x03              | R3(STATUS 状态寄存器)       | 保留                       |

| 0x04              | R4/FSR(RAM 选择寄存器)      | 保留                       |

| 0x05              | 保留                     | 保留                       |

| 0x06              | R6/PORT6(数据寄存器)        | IOC6/P6CR (P6 方向控制寄存器)   |

| 0x07              | 保留                     | IOC7/HDSOCR(驱动增强控制寄存器 0) |

| 0x08              | R8/PWMCON(PWM 控制寄存器)   | IOC8/HDS1CR(驱动增强控制寄存器 1) |

| 0x09              | R9/PRD(PWM 周期寄存器)      | IOC9/PHDCR(端口上下拉控制寄存器)   |

| 0x0A              | RA/PDT1(PWM1 占空比寄存器)   | IOCA/HDS2CR(驱动增强控制寄存器 2) |

| 0x0B              | RB/PDT2(PWM2 占空比寄存器)   | IOCB/PDCR (端口下拉控制寄存器)    |

| 0x0C              | RC/PDT3(PWM3 占空比寄存器)   | IOCC/ODCR (P6 开漏控制寄存器)   |

| 0x0D              | RD/ICIECR(输入变化中断使能寄存器) | IOCD/PHCR (P6 端口上拉控制寄存器) |

| 0x0E              | RE/CPUCON(CPU 模式控制寄存器) | IOCE/WDE(WDT 控制寄存器)      |

| 0x0F              | RF/RIFG(中断标志寄存器)       | IOCF/RIEN (中断使能控制寄存器)    |

| 0x10<br>-<br>0x3F | 通用寄存器                  |                          |

# 3 功能模块

# 3.1 操作寄存器

# 3.1.1 RPAGE~RO-IAR(间接地址存储器)

| Bit 7     | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|-----------|------|-------|-------|-------|-------|-------|-------|--|--|

| RIND<7:0> |      |       |       |       |       |       |       |  |  |

间接寻址寄存器并不是一个实际存在的寄存器,它的主要功能是作为间接寻址的指针。 任何以 RO 作为指针的指令,实际对应的地址是 R4 (RAM 选择寄存器)低 6 位 FSR<5:0>所指 向的数据。

#### 3.1.2 RPAGE~R1-TCC(TCC 定时计数器)

| Bit 7    | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|----------|------|-------|-------|-------|-------|-------|-------|--|--|

| TCC<7:0> |      |       |       |       |       |       |       |  |  |

TCC 是一个 8Bit 上行计数器,时钟源可选内部时钟/外部时钟,计数溢出可形成中断,TCC 可读可写。

TCC 可由 EXINT 引 上的信号边沿或指令周期触发产生加 1 操作(CONT. 4 位定义)。如果清零 PAB 位(CONT. 3),会有一个预分频器分配给 TCC,当 TCC 寄存器被写入一个值时,预分频器的值会被清 0。

#### 3.1.3 RPAGE~R2-PCL(PC 程序计数器)

| Bit 7    | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|----------|------|-------|-------|-------|-------|-------|-------|--|

| PCL<7:0> |      |       |       |       |       |       |       |  |

程序计数器 (PC) 是用于记录每个指令周期中 CPU 所要处理的指令的指针。在 CPU 运行周期中,PC 将指令指针推进程序存储器,然后指针自增 1 以进入下一个周期。

程序计数器 (PC) 是用于记录每个指令周期中 CPU 所要处理的指令的指针。在 CPU 运行周期中, PC 将指令指针推进程序存储器, 然后指针自增 1 以进入下一个周期。JZ8P1525 拥有一个 10 位宽度的程序计数器 (PC), 其低字节来自可读写的 PCL, 高位 (PC<9:8>) 不可读。

JZ8P1525 堆栈是用于记录程序返回的指令指针。当调用子程序时,PC 将指令指针压栈。 待执行返回指令时,堆栈将指令指针送回 PC,继续进行原来的进程。JZ8P1525 拥有 5 级堆栈, 该堆栈既不占程序存储空间也不占数据存储空间,并且堆栈指针不能读写。

- (1) 寄存器 PC 和内置 5 级堆栈都是 10 位宽,用于 1K×14Bit ROM 的寻址,JZ8P1525 程序存储区映射。

- (2) 一般情况下, PC 自增一; 复位时, PC 的所有位都被清零。

- (3) 指令"JMP"允许直接载入低 10 位地址,因此,JMP 指令可以实现当前页面内(1K 范围内)任意位置跳转。指令"JMP" 直接载入低 10 位地址,同时将 PC +1 压栈,子程序入口地址只要在同一页面内就能够被准确定位。

晶哲科技 改变从芯开始

第 12 页 共 54 页

- (4) 执行"RET"指令时将栈顶数据送到 PC。

- (5) 当设置 PC 查表能力为 1/4K 时(设置 OPTION 选项中查表范围 为 0~256),任何对 PC 的内容进行直接修改的指令都将引起 PC 的第 9、10 位被清零。因此,产生的跳转限于同一页面的前 256 个地址,改变 PC 内容的指令需要 2 个指令周期。

当设置 PC 查表能力为 1K 时,任何对 PC 值进行改写的指令会相应影响 PC 最高两位。因此,产生的跳转可扩充至 1K 范围。

- (6) 发生中断时,程序计数器的值将发生改变,PC 赋值为008。

- (7) 堆栈的工作犹如循环缓冲器,也就是说,压栈 5 次之后,第 6 次压栈时进栈的数据将覆盖第 1 次进栈的数据,而第 7 次压栈时进栈的数据将覆盖第 2 次进栈的数据,依此类推。

# 3.1.4 RPAGE~R3-STATUS(STATUS 状态寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| RST   | GB1  | GB0   | T     | Р     | Z     | DC    | С     |

Bit<7>:RST-复位类型标志位:

0:其它复位类型

1:引脚状态改变引起唤醒

Bit<6:5>:GB1-GB0:通用读写位

Bit<4>:T-时间溢出位

0:WDT 溢出

1:执行"SLEEP"和"CWDT"指令或低压复位

影响 T/P 的事件如下表所示:

| 类型           | RST | Т  | Р  |

|--------------|-----|----|----|

| 上电复位         | 0   | 1  | 1  |

| 工作模式下按 RESET | 0   | 保持 | 保持 |

| RESET 唤醒     | 0   | 1  | 0  |

| 工作模式下 WDT 溢出 | 0   | 0  | 保持 |

| WDT 溢出唤醒     | 0   | 0  | 0  |

| 端口状态变化唤醒     | 1   | 1  | 0  |

| 执行 WDTC 指令   | 保持  | 1  | 1  |

| 执行 SLEEP 指令  | 保持  | 1  | 0  |

Bit<3>:P-掉电标志位:

0:执行 "SLEEP" 指令

1:上电复位或执行 "CWDT" 指令

Bit<2>:Z-零标志位算术或逻辑操作结果为零时置为"1"

0: 当算术或者逻辑运算结果不为 0

1: 当算术或者逻辑运算结果为0

晶哲科技 改变从芯开始

第 13 页 共 54 页

#### Bit<1>:DC-辅助进位标志:

0:执行加法运算时,低四位没有进位产生;/执行减法运算时,低四位产生借位

1:执行加法运算时,低四位有进位产生;/执行减法运算时,低四位没产生借位

#### Bit<0>:C-进位标志:

0:执行加法运算时, 高四位没有进位产生; /执行减法运算时, 高四位产生借位

1:执行加法运算时, 高四位有进位产生: /执行减法运算时, 高四位没产生借位

#### 3.1.5 RPAGE~R4-RSR(FSR RAM 选择寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit O |  |

|-------|------|-------|----------|-------|-------|-------|-------|--|

| 1     | 1    |       | FSR<5:0> |       |       |       |       |  |

FSR<5:0> 在间接寻址方式中用于选择 RAM 寄存器地址 (寻址范围:0X00~0X3F)

FSR 用于配合 RO 实现间接寻址操作。用户可以将某个寄存器对应的地址放进 FSR, 然后通过访问间接寻址寄存器 RO, 此时地址将指向 FSR 中对应地址的寄存器。

#### 3.1.6 RPAGE~R6-PORT6(PORT6 数据寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| _     | _    | P65   | P64   | P63   | P62   | P61   | P60   |

端口输入/输出寄存器, P6 端口为 8 位 , R6 为可读可写寄存器

# 3.1.7 RPAGE~R8-PWMCON(PWM 控制寄存器)

| Bit 7 | Bit6   | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1      | Bit 0 |

|-------|--------|--------|--------|--------|-------|------------|-------|

| T1EN  | PWM3EN | PWM2EN | PWM1EN | T1PTEN |       | T1PSR<2:0> |       |

Bit<7>:T1EN-T1/PWM 计数器使能

1:使能

0:禁止

若设置 PRD 寄存器, T1 计数到 PRD 预设值复位, T1 从 1 开始计数。

Bit<6>:PWM3EN-PWM3 输出使能控制位

1:使能 (P60 输出 PWM3)

0:禁止

Bit<5>:PWM2EN-PWM2 输出使能控制位

1:使能 (P61 输出 PWM2)

0:禁止

Bit<4>:PWM1EN-PWM1 输出使能控制位

1:使能 (P62 输出 PWM1)

0:禁止

Bit<3>:T1PTEN -T1 预分频选择控制位

1:使能

0:禁止

晶哲科技 改变从芯开始

第 14 页 共 54 页

Bit<2:0>:T1PSR<2:0>-分频系数选择位:

| T1PTEN | T1PSR<2> | T1PSR<1> | T1PSR<0> | T1 分频比 |

|--------|----------|----------|----------|--------|

| 0      | 0        | 0        | 0        | 1:1    |

| 1      | 0        | 0        | 0        | 1:2    |

| 1      | 0        | 0        | 1        | 1:4    |

| 1      | 0        | 1        | 0        | 1:8    |

| 1      | 0        | 1        | 1        | 1:16   |

| 1      | 1        | 0        | 0        | 1:32   |

| 1      | 1        | 0        | 1        | 1:64   |

| 1      | 1        | 1        | 0        | 1:128  |

| 1      | 1        | 1        | 1        | 1:256  |

#### 3.1.8 RPAGE~R9-PRD(PWM 周期寄存器)

| Bit 7    | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|----------|------|-------|-------|-------|-------|-------|-------|--|

| PRD<7:0> |      |       |       |       |       |       |       |  |

T1/PWM 周期寄存器

#### 3.1.9 RPAGE~RA-PDC1(PWM1 占空比寄存器)

| Bit 7 | Bit6      | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|-------|-----------|-------|-------|-------|-------|-------|-------|--|--|

|       | PDC1<7:0> |       |       |       |       |       |       |  |  |

Bit<7:0>:PDC1<7:0>-PWM1 占空比

#### 3.1.10 RPAGE~RB-PDC2(PWM2 占空比寄存器)

| Bit 7     | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-----------|------|-------|-------|-------|-------|-------|-------|--|

| PDC2<7:0> |      |       |       |       |       |       |       |  |

Bit<7:0>:PDC2<7:0>-PWM2 占空比

# 3.1.11 RPAGE~RC-PDC3(PWM3 占空比寄存器)

| Bit 7     | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-----------|------|-------|-------|-------|-------|-------|-------|--|

| PDC3<7:0> |      |       |       |       |       |       |       |  |

Bit<7:0>:PDC3<7:0>-PWM3 占空比

# 3.1.12 RPAGE~RD-ICIECR(P6端口中断唤醒使能寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------|------|---------|---------|---------|---------|---------|---------|

| 0     | 0    | P6WK<5> | P6WK<4> | P6WK<3> | P6WK<2> | P6WK<1> | P6WK<0> |

Bit<5:0>:P6WK<5:0>-P6 端口中断唤醒使能

1:使能

0:禁止(默认)

注意:在 OPTION 中端口唤醒设置选择中,如果选择 P6 端口非独立控制,则端口唤醒不受 RD 寄存器控制,否则需要对 RD 寄存器做处理,不然端口无法唤醒。

# 3.1.13 RPAGE~RE-CPUCON(CPU 模式控制寄存器)

| Bit 7 | Bit6   | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------|--------|-------|-------|-------|-------|-------|

| IPWM1 | PWMCKS | TCCCKS | PWMWE | TCCWE | STPHX | CLKMD | IDLE  |

Bit<7>: IPWM1-PWM 互补输出

1:PWM1 输出取反

0:PWM1 输出无取反

Bit<6>:PWMCKS-PWM 时钟源

1:选择系统时钟

0:选择指令周期时钟

Bit<5>:TCCCKS-TCC 时钟源选择

1:选择系统时钟

0:选择指令周期时钟

Bit<4>:PWMWE-PWM 唤醒

1:PWM 唤醒使能,可唤醒空闲模式

0:PWM 唤醒禁止

Bit<3>:TCCWE-TCC 唤醒

1:TCC 唤醒使能,可唤醒空闲模式,RTC 模式下可唤醒睡眠以及空闲模式

0:TCC 唤醒禁止

(RTC 模式下设置 TCCWE=1&RTCS=1 休眠时 LXT 继续工作不会停止,否则时休眠会停止 LXT)

Bit<2>:STPHX-高速时钟

1:停止高速时钟,包括 IRC 和晶振振荡器时钟(不包括 RTC 时钟)

0:高速时钟正常工作

Bit<1>:CLKMD-系统时钟

1: 系统时钟使用低速 RC 振荡器时钟

0: 系统时钟使用高速 IRC 或者晶振振荡器时钟

(系统从正常模式进入低速模式时 先设置 CLKMD=1, 后设置 STPHX=1,

系统从低速模式进入正常模式时 先设置 STPHX=0, 后设置 CLKMD=0)

Bit<0>: IDLE-空闲模式

1: 系统执行 SLEEP 指令时进入空闲模式,系统时钟正常工作 (TCC 和 PWM 在空闲模式下如果选择系统时钟可继续工作,并可唤醒系统)

0: 系统执行 SLEEP 指令时进入睡眠模式

# 3.1.14 RPAGE~RF-ISR(中断标志寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| 0     | 0    | 0     | 0     | T1IF  | EXIF  | ICIF  | TCIF  |

Bit<3>:T1IF-T1/PWM 周期中断标志位,软件清 0

Bit<2>:EXIF-外部端口中断标志位(由EXINT引脚上升沿或者下降沿置1,软件清0)

Bit<1>:ICIF-P6端口状态改变中断标志位,软件清0

Bit<0>:TCIF-TCC 中断标志位,软件清 0

1:有中断

0:无中断

注意:清除中断标志位时,必须使用 MOV RF, A 操作,不能使用 BTC 和 AND RF, A 指令操作。

# 3.2 控制寄存器

#### 3.2.1 CONT (控制寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| RTCS  | INT  | TS    | TE    | PAB   | PSR2  | PSR1  | PSR0  |

Bit<7>:RTCS-TCC 信号源选择

1:选择外部晶振时钟(LXT的4分频)

0:TCC 时钟由 TCCCKS 和 TS 决定, TCCCKS=1 时钟源选择 FOSC, TCCCKS=0 时钟源由 TS 决定(TCC 时钟源优先级 RTCS>TCCCKS>TS)

注意: 当 OPTION 选项 RTC 选择使能时有效, 否则 Bit7 为通用读写位。

Bit<6>: INT-中断使能标志位

0:由指令或硬件禁止中断

1:由指令使能中断

Bit<5>:TS-TCC 信号源选择位

0:内部指令周期时钟

1:外部输入信号(P62 需要设置为输入口)

Bit<4>:TE-TCC 信号边沿选择位

0:TCC 引脚信号发生由低到高变化加 1

1:TCC 引脚信号发生由高到低变化加 1

Bit<3>:PAB-预分频器分配位

0:预分频器分给 TCC

1:预分频器分给 WDT

Bit<2:0>PSR2~PSR0:TCC/WDT 预分频选择控制位:

| PSR2 | PSR1 | PSR0 | TCC 分频系数 | WDT 分频系数 |

|------|------|------|----------|----------|

| 0    | 0    | 0    | 1:2      | 1:1      |

| 0    | 0    | 1    | 1:4      | 1:2      |

| 0    | 1    | 0    | 1:8      | 1:4      |

| 0    | 1    | 1    | 1:16     | 1:8      |

| 1    | 0    | 0    | 1:32     | 1:16     |

| 1    | 0    | 1    | 1:64     | 1:32     |

| 1    | 1    | 0    | 1:128    | 1:64     |

| 1    | 1    | 1    | 1:256    | 1:128    |

CONT 为可读可写寄存器

注意:CONT 寄存器 Bit. 2~0 (PSR2~PSR0) 分频选择位在切换状态时,需先关闭看门狗使能,待切换完成后再打开看门狗使能,否则容易导致复位。

# 3.2.2 IOPAGE~IOC6-P6CR(P6 方向控制寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------|------|---------|---------|---------|---------|---------|---------|

| 1     | 1    | P6CR<5> | P6CR<4> | P6CR<3> | P6CR<2> | P6CR<1> | P6CR<0> |

Port6 方向控制位

1:输入(默认)

0:输出

# 3.2.3 IOPAGE~IOC7-HDSOCR(驱动增强控制寄存器 0)

| Bit 7   | Bit6     | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    |

|---------|----------|----------|----------|---------|----------|----------|----------|

| P63HSEN | P60HS<2> | P60HS<1> | P60HS<0> | P63HDEN | P60HD<2> | P60HD<1> | P60HD<0> |

Bit<7>:P63HSEN-P63 灌电流增强使能位:

1:使能

0:禁止

Bit<6:4>:P60HS<2:0>-P60 灌电流增强选择

| P60HS<2> | P60HS<1> | P60HS<0> | 增强等级  |

|----------|----------|----------|-------|

| 0        | 0        | 0        | 无增强   |

| 0        | 0        | 1        | 40mA  |

| 0        | 1        | 0        | 60mA  |

| 0        | 1        | 1        | 80mA  |

| 1        | 0        | 0        | 100mA |

| 1        | 0        | 1        | 120mA |

Bit<3>:P63HDEN-P63 拉电流增强使能

1:使能

0:禁止

Bit<2:0>:P60HD<2:0>-P60 拉电流增强选择

| P60HD<2> | P60HD<1> | P60HD<0> | 增强等级  |

|----------|----------|----------|-------|

| 0        | 0        | 0        | 无增强   |

| 0        | 0        | 1        | 40mA  |

| 0        | 1        | 0        | 60mA  |

| 0        | 1        | 1        | 80mA  |

| 1        | 0        | 0        | 100mA |

| 1        | 0        | 1        | 120mA |

# 3.2.4 IOPAGE~IOC8-HDS1CR(驱动增强控制寄存器 1)

| Bit 7   | Bit6     | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    |

|---------|----------|----------|----------|---------|----------|----------|----------|

| P64HSEN | P61HS<2> | P61HS<1> | P61HS<0> | P64HDEN | P61HD<2> | P61HD<1> | P61HD<0> |

Bit<7>:P64HSEN-P64 灌电流增强使能位:

1:使能

0:禁止

晶哲科技 改变从芯开始

第 19 页 共 54 页

Bit<6:4>:P61HS<2:0>-P61 灌电流增强选择

| P61HS<2> | P61HS<1> | P61HS<0> | 增强等级  |

|----------|----------|----------|-------|

| 0        | 0        | 0        | 无增强   |

| 0        | 0        | 1        | 40mA  |

| 0        | 1        | 0        | 60mA  |

| 0        | 1        | 1        | 80mA  |

| 1        | 0        | 0        | 100mA |

| 1        | 0        | 1        | 120mA |

Bit<3>:P64HDEN-P64 拉电流增强使能

1:使能

0:禁止

Bit<2:0>:P61HD<2:0>-P61 拉电流增强选择

| P61HD<2> | P61HD<1> | P61HD<0> | 增强等级  |

|----------|----------|----------|-------|

| 0        | 0        | 0        | 无增强   |

| 0        | 0        | 1        | 40mA  |

| 0        | 1        | 0        | 60mA  |

| 0        | 1        | 1        | 80mA  |

| 1        | 0        | 0        | 100mA |

| 1        | 0        | 1        | 120mA |

# 3.2.5 IOPAGE~IOC9-PHDCR(端口上下拉控制寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|---------|---------|-------|-------|-------|-------|

| 1     | 1    | P6PD<5> | P6PD<4> | 1     | 1     | 1     | 1     |

Bit<5:4>:P6<5:4>下拉使能控制

0:使能

1:禁止(默认)

注意: 当 OPTION 选项 P6 上下拉控制选择使能时有效,否则全部读为 1。

# 3.2.6 IOPAGE~IOCA-HDS2CR(驱动增强控制寄存器 2)

| Bit 7   | Bit6     | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit O    |

|---------|----------|----------|----------|---------|----------|----------|----------|

| P65HSEN | P62HS<2> | P62HS<1> | P62HS<0> | P65HDEN | P62HD<2> | P62HD<1> | P62HD<0> |

Bit<7>:P65HSEN-P65 灌电流增强使能位:

1:使能

0:禁止

Bit<6:4>:P62HS<2:0>-P62 灌电流增强选择

| P62HS<2> | P62HS<1> | P62HS<0> | 增强等级 |

|----------|----------|----------|------|

| 0        | 0        | 0        | 无增强  |

| 0        | 0        | 1        | 40mA |

| 0        | 1        | 0        | 60mA |

晶哲科技 改变从芯开始

第 20 页 共 54 页

| 0 | 1 | 1 | 80mA  |

|---|---|---|-------|

| 1 | 0 | 0 | 100mA |

| 1 | 0 | 1 | 120mA |

Bit<3>:P65HDEN-P65 拉电流增强使能

1:使能 0:禁止

Bit<2:0>:P62HD<2:0>-P62 拉电流增强选择

| _ |          |          |          |       |  |  |  |  |

|---|----------|----------|----------|-------|--|--|--|--|

|   | P62HD<2> | P62HD<1> | P62HD<0> | 增强等级  |  |  |  |  |

|   | 0        | 0        | 0        | 无增强   |  |  |  |  |

|   | 0        | 0        | 1        | 40mA  |  |  |  |  |

|   | 0        | 1        | 0        | 60mA  |  |  |  |  |

|   | 0        | 1        | 1        | 80mA  |  |  |  |  |

|   | 1        | 0        | 0        | 100mA |  |  |  |  |

| Ī | 1        | 0        | 1        | 120mA |  |  |  |  |

# 3.2.7 IOPAGE~IOCB-PDCR(端口下拉控制寄存器)

| Bit 7   | Bit6    | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|---------|---------|-------|-------|-------|-------|

| P6PD<3> | P6PD<2> | P6PD<1> | P6PD<0> | 1     | 1     | 1     | 1     |

Bit<7:4>:P6<3:0>下拉使能控制

1:禁止

0:使能

注:P6PH<3>软件下拉,需在 option 设置时使能 P6 上下拉控制使能才能有效,否则读为 1。

# 3.2.8 IOPAGE~IOCC-ODCR(P6 开漏控制寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------|------|---------|---------|---------|---------|---------|---------|

| _     | _    | P60D<5> | P60D<4> | P60D<3> | P60D<2> | P60D<1> | P60D<0> |

Bit<5:0>:P60D<5:0>-P6 开漏输出使能

1:使能

0:禁止

# 3.2.9 IOPAGE~IOCD-PHCR(P6 端口上拉控制寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------|------|---------|---------|---------|---------|---------|---------|

| 1     | 1    | P6PH<5> | P6PH<4> | P6PH<3> | P6PH<2> | P6PH<1> | P6PH<0> |

Port6 上拉控制

0:使能

1:禁止(默认)

注:P6PH<3>软件上拉,需在 option 设置时使能 P6 上下拉才能有效,否则读为 1。

晶哲科技 改变从芯开始

第 21 页 共 54 页

# 3.2.10 IOPAGE~IOCE-WDTCR(看门狗控制寄存器)

| Bit 7 | Bit6 | Bit 5    | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

|-------|------|----------|----------|----------|-------|-------|-------|

| WDTEN | EIS  | P6WDS<5> | P6WDS<4> | P6WDS<3> | PWM3S | PWM2S | PWM1S |

Bit<7>: WDTEN-WDT 使能控制位

1:使能

0:禁止

Bit<6>:EIS-P60 外部中断端口使能位

1:使能,在这种情况下,P60的 I/O 控制位(P6CR的 BitO)必须设为"1",管脚的状态可以由P6端口读取,P60下降沿触发外部中断

0:禁止, P60 为双向 I/0 管脚, EXINT 通道被屏蔽

Bit<5>:P6WDS<5>-P65 口弱驱动使能控制位

1:使能

0:禁止

Bit<4>:P6WDS<4>-P64 口弱驱动使能控制位

1:使能

0:禁止

Bit<3>:P6WDS<3>-P63 口弱驱动使能控制位

1:使能

0:禁止

Bit<2>:PWM3S-PWM3 输出脚位映射选择位

1:PWM3 映射至 P65 口

0:PWM3 映射至 P60 口

Bit<1>:PWM2S-PWM2 输出脚位映射选择位

1:PWM2 映射至 P64 口

0:PWM2 映射至 P61 口

Bit<0>:PWM1S-PWM1 输出脚位映射选择位

1:PWM1 映射至 P63 口

0:PWM1 映射至 P62 口

# 3.2.11 IOPAGF~IOCF-IMR(中断使能控制寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| 0     | 0    | 0     | 0     | T1IE  | EXIE  | ICIE  | TCIE  |

Bit<3>:T1IE-T1 中断使能位

1:使能

0:禁止

Bit<2>:EXIE-外部中断使能控制

晶哲科技 改变从芯开始

第 22 页 共 54 页

1:使能

0:禁止

Bit<1>:ICIE-P6 端口状态改变中断使能控制

1:使能

0:禁止

Bit<0>:TCIE-TCC 溢出中断使能控制

1:使能

0:禁止

# 3.3 GPIO 功能模块

JZ8P1525 有 1 组双向 I/0 端口, 共 6 个输入, 6 个输出。

- 6个可编程上拉 I/0 引脚:P6.0~P6.5;

- 6个可编程下拉 I/O 引脚:P6.0~P6.5;

- 3个可程序配置驱动增强/弱驱动引脚:P63~P65; (弱驱动模式下拉灌电流理论 4mA/1mA)

- 3个可程序配置五级驱动增强引脚:P60、P61、P62; (驱动增强拉灌电流最大可选 120mA)

- 6个可编程驱动增强 I/O 引脚:P6.0~P6.5;

端口输入特性表格如下(仅作参考):

| 端口          | SMT             | HSMT              | EMT              | INV      |

|-------------|-----------------|-------------------|------------------|----------|

| P6. 3       | 0.56*VDD        | 0.2*VDD/0.8*VDD   | 0.2*VDD/0.35*VDD | 0.54*VDD |

| P6.0∼P6.2   | 0.2*VDD/0.6*VDD | 0. 2*VDD/0. 8*VDD | 0.2*VDD/0.35*VDD | 0.54*VDD |

| P6. 4∼P6. 5 | 0.2*VDD/0.6*VDD | 0.2*VDD/0.8*VDD   | 0.36*VDD         | 0.54*VDD |

#### 以上参数仅做参考,请以目标样机实测数据为准。

#### 3.3.1 GPIO 寄存器说明

#### RPAGE~R6-PORT6 (PORT6 数据寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| 0     | 0    | P65   | P64   | P63   | P62   | P61   | P60   |

端口输入/输出寄存器, P6 端口为 8 位 , R6 为可读可写寄存器

#### IOPAGE~IOC6-P6CR(P6 方向控制寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------|------|---------|---------|---------|---------|---------|---------|

| 1     | 1    | P6CR<5> | P6CR<4> | P6CR<3> | P6CR<2> | P6CR<1> | P6CR<0> |

Port6 端口输入/输出设置寄存器

1:输入(默认)

0:输出

# IOPAGE~IOC7-HDSOCR(驱动增强控制寄存器 0)

| Bit 7   | Bit6     | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    |

|---------|----------|----------|----------|---------|----------|----------|----------|

| P63HSEN | P60HS<2> | P60HS<1> | P60HS<0> | P63HDEN | P60HD<2> | P60HD<1> | P60HD<0> |

Bit<7>:P63HSEN-P63 灌电流增强使能位:

1:使能

0:禁止

Bit<6:4>:P60HS<2:0>-P60 灌电流增强选择

| P60HS<2> | P60HS<1> | P60HS<0> | 增强等级  |

|----------|----------|----------|-------|

| 0        | 0        | 0        | 无增强   |

| 0        | 0        | 1        | 40mA  |

| 0        | 1        | 0        | 60mA  |

| 0        | 1        | 1        | 80mA  |

| 1        | 0        | 0        | 100mA |

晶哲科技 改变从芯开始

第 24 页 共 54 页

| 1 | 0 | 1 | 120mA |

|---|---|---|-------|

|   |   |   |       |

Bit<3>:P63HDEN-P63 拉电流增强使能

1:使能 0:禁止

Bit<2:0>:P60HD<2:0>-P60 拉电流增强选择

| ٦. |          |          |          |       |  |  |  |  |  |  |  |

|----|----------|----------|----------|-------|--|--|--|--|--|--|--|

|    | P60HD<2> | P60HD<1> | P60HD<0> | 增强等级  |  |  |  |  |  |  |  |

|    | 0        | 0        | 0        | 无增强   |  |  |  |  |  |  |  |

|    | 0        | 0        | 1        | 40mA  |  |  |  |  |  |  |  |

|    | 0        | 1        | 0        | 60mA  |  |  |  |  |  |  |  |

|    | 0        | 1        | 1        | 80mA  |  |  |  |  |  |  |  |

|    | 1        | 0        | 0        | 100mA |  |  |  |  |  |  |  |

| Ī  | 1        | 0        | 1        | 120mA |  |  |  |  |  |  |  |

# IOPAGE~IOC8-HDS1CR(驱动增强控制寄存器 1)

| Bit 7   | Bit6     | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    |

|---------|----------|----------|----------|---------|----------|----------|----------|

| P64HSEN | P61HS<2> | P61HS<1> | P61HS<0> | P64HDEN | P61HD<2> | P61HD<1> | P61HD<0> |

Bit<7>:P64HSEN-P64 灌电流增强使能位:

1:使能

0:禁止

Bit<6:4>:P61HS<2:0>-P61 灌电流增强选择

| P61HS<2> | P61HS<1> | P61HS<0> | 增强等级  |

|----------|----------|----------|-------|

| 0        | 0        | 0        | 无增强   |

| 0        | 0        | 1        | 40mA  |

| 0        | 1        | 0        | 60mA  |

| 0        | 1        | 1        | 80mA  |

| 1        | 0        | 0        | 100mA |

| 1        | 0        | 1        | 120mA |

Bit<3>:P64HDEN-P64 拉电流增强使能

1:使能

0:禁止

Bit<2:0>:P61HD<2:0>-P61 拉电流增强选择

| P61HD<2> | P61HD<1> | P61HD<0> | 增强等级  |

|----------|----------|----------|-------|

| 0        | 0        | 0        | 无增强   |

| 0        | 0        | 1        | 40mA  |

| 0        | 1        | 0        | 60mA  |

| 0        | 1        | 1        | 80mA  |

| 1        | 0        | 0        | 100mA |

| 1        | 0        | 1        | 120mA |

#### IOPAGE~IOC9-PHDCR(端口上下拉控制寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|---------|---------|-------|-------|-------|-------|

| 1     | 1    | P6PD<5> | P6PD<4> | 1     | 1     | 1     | 1     |

Bit<5:4>:P6<5:4>下拉使能控制

0:使能

1:禁止(默认)

注意: 当 OPTION 选项 P6 上下拉控制选择使能时有效, 否则全部读为 1。

#### IOPAGE~IOCA-HDS2CR(驱动增强控制寄存器 2)

|   | Bit 7  | Bit6     | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    |

|---|--------|----------|----------|----------|---------|----------|----------|----------|

| P | 65HSEN | P62HS<2> | P62HS<1> | P62HS<0> | P65HDEN | P62HD<2> | P62HD<1> | P62HD<0> |

Bit<7>:P65HSEN-P65 灌电流增强使能位:

1:使能

0:禁止

Bit<6:4>:P62HS<2:0>-P62 灌电流增强选择

| P62HS<2> | P62HS<1> | P62HS<0> | 增强等级  |

|----------|----------|----------|-------|

| 0        | 0        | 0        | 无增强   |

| 0        | 0        | 1        | 40mA  |

| 0        | 1        | 0        | 60mA  |

| 0        | 1        | 1        | 80mA  |

| 1        | 0        | 0        | 100mA |

| 1        | 0        | 1        | 120mA |

Bit<3>:P65HDEN-P65 拉电流增强使能

1:使能

0:禁止

Bit<2:0>:P62HD<2:0>-P62 拉电流增强选择

| P62HD<2> | P62HD<1> | P62HD<0> | 增强等级  |

|----------|----------|----------|-------|

| 0        | 0        | 0        | 无增强   |

| 0        | 0        | 1        | 40mA  |

| 0        | 1        | 0        | 60mA  |

| 0        | 1        | 1        | 80mA  |

| 1        | 0        | 0        | 100mA |

| 1        | 0        | 1        | 120mA |

#### IOPAGE~IOCB-PDCR(端口下拉控制寄存器)

| Bit 7   | Bit6    | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|---------|---------|-------|-------|-------|-------|

| P6PD<3> | P6PD<2> | P6PD<1> | P6PD<0> | 1     | 1     | 1     | 1     |

Bit<7:4>:P6<3:0>下拉使能控制

晶哲科技 改变从芯开始

第 26 页 共 54 页

1:禁止

0:使能

注:P6PH<3>软件下拉,需在 option 设置时使能 P6 上下拉控制使能才能有效,否则读为 1。 IOPAGE~IOCC-ODCR(P6 开漏控制寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------|------|---------|---------|---------|---------|---------|---------|

| _     | _    | P60D<5> | P60D<4> | P60D<3> | P60D<2> | P60D<1> | P60D<0> |

Bit<5:0>:P60D<5:0>-P6 开漏输出使能

1:使能

0:禁止

# IOPAGE~IOCD-PHCR(P6端口上拉控制寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------|------|---------|---------|---------|---------|---------|---------|

| 1     | 1    | P6PH<5> | P6PH<4> | P6PH<3> | P6PH<2> | P6PH<1> | P6PH<0> |

Port6 上拉控制

0:使能

1:禁止(默认)

注:P6PH<3>软件上拉,需在 option 设置时使能 P6 上下拉才能有效,否则读为 1。

# 3.4 TCC 定时器功能模块

JZ8P1525 提供一个 8 位计数器作为 TCC 和 WDT 的预分频器。预分频器在同一时间内仅供 TCC 或仅供 WDT 使用,且由 CONT 寄存器里的 PAB 位来决定预分频器的分配。PSR0 ~PSR2 三位决定预分频比。在 TCC 模式下每次 TCC 被写入一个值,预分频寄存器就被清零。当预分频器分配到 WDT 模式,当执行"CWDT"或"SLEEP"指令时,WDT 和预分频寄存器的值被清零。如果预分频器先分配给 TCC 然后分配给 WDT,预分频计数器的内容将自动清除,反之亦然。

TCC (R1)是一个8Bit上行计数器,只要有时钟就工作。时钟源既可以是内部系统时钟(上升沿触发),也可以选择外部时钟(由TCC引脚输入,触发沿可选),如果没有分频控制,每个时钟(Fm/Fs)周期(选择内部时钟)或每个外部时钟周期(外部时钟),计数器实现加1。系统提供一个8Bit计数器作为TCC的预分频器。可以通过CONT寄存器设置TCC预分频、触发沿、时钟等。

TCC 计数溢出可以形成中断信号。

在 IDLE 模式下,TCC 中断可以唤醒电路,唤醒后可以选择进中断或者继续执行原程序,方法参考端口状态变化唤醒。

注意:清除中断标志位时,必须使用 MOV RF, A 操作,不能使用 BTC 和 AND RF, A 指令操作。

# 3.4.1 TCC 定时器寄存器说明

CONT (控制寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| RTCS  | INT  | TS    | TE    | PAB   | PSR2  | PSR1  | PSR0  |

Bit<7>:RTCS-TCC 信号源选择

1:选择外部晶振时钟(LXT的4分频)

0:TCC 时钟由 TCCCKS 和 TS 决定, TCCCKS=1 时钟源选择 FOSC, TCCCKS=0 时钟源由 TS 决定(TCC 时钟源优先级 RTCS>TCCCKS>TS)

#### 注意: 当 OPTION 选项 RTC 选择使能时有效,否则 Bit7 为通用读写位。

Bit<5>:TS-TCC 信号源选择位

0:内部指令周期时钟

1:外部输入信号(P62需要设置为输入口)

Bit<4>:TE-TCC 信号边沿选择位

0:TCC 引脚信号发生由低到高变化加 1

1:TCC 引脚信号发生由高到低变化加 1

Bit<3>:PAB-预分频器分配位

0:预分频器分给 TCC

1:预分频器分给 WDT

晶哲科技 改变从芯开始

第 28 页 共 54 页

Bit<2:0>PSR2~PSR0:TCC/WDT 预分频选择控制位:

| PSR2 | PSR1 | PSR0 | TCC 分频系数 | WDT 分频系数 |

|------|------|------|----------|----------|

| 0    | 0    | 0    | 1:2      | 1:1      |

| 0    | 0    | 1    | 1:4      | 1:2      |

| 0    | 1    | 0    | 1:8      | 1:4      |

| 0    | 1    | 1    | 1:16     | 1:8      |

| 1    | 0    | 0    | 1:32     | 1:16     |

| 1    | 0    | 1    | 1:64     | 1:32     |

| 1    | 1    | 0    | 1:128    | 1:64     |

| 1    | 1    | 1    | 1:256    | 1:128    |

CONT 为可读可写寄存器

注意:CONT 寄存器 Bit. 2~0 (PSR2~PSR0) 分频选择位在切换状态时,需先关闭看门狗使能,待切换完成后再打开看门狗使能,否则容易导致复位。

RPAGE~R1-TCC(TCC 定时计数器)

| Bit 7 | Bit6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|-------|----------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|       | TCC<7:0> |       |       |       |       |       |       |  |  |  |  |

TCC 是一个 8Bit 上行计数器,时钟源可选内部时钟/外部时钟,计数溢出可形成中断,TCC 可读可写。

#### RPAGE~RE-CPUCON(CPU 模式控制寄存器)

| Bit 7 | Bit6   | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------|--------|-------|-------|-------|-------|-------|

| IPWM1 | PWMCKS | TCCCKS | PWMWE | TCCWE | STPHX | CLKMD | IDLE  |

Bit<5>:TCCCKS-TCC 时钟源选择

1:选择系统时钟

0:选择指令周期时钟

Bit<3>:TCCWE-TCC 唤醒

- 1:TCC 唤醒使能,可唤醒空闲模式,RTC 模式下可唤醒睡眠以及空闲模式

- 0:TCC 唤醒禁止

(RTC 模式下设置 TCCWE=1&RTCS=1 休眠时 LXT 继续工作不会停止,否则时休眠会停止 LXT)

Bit<2>:STPHX-高速时钟

- 1:停止高速时钟,包括 IRC 和晶振振荡器时钟(不包括 RTC 时钟)

- 0:高速时钟正常工作

Bit<1>:CLKMD-系统时钟

- 1: 系统时钟使用低速 RC 振荡器时钟

- 0: 系统时钟使用高速 IRC 或者晶振振荡器时钟

- (系统从正常模式进入低速模式时 先设置 CLKMD=1, 后设置 STPHX=1,

系统从低速模式进入正常模式时 先设置 STPHX=0, 后设置 CLKMD=0)

晶哲科技 改变从芯开始

第 29 页 共 54 页

Bit<0>:IDLE-空闲模式

1: 系统执行 SLEEP 指令时进入空闲模式,系统时钟正常工作

(TCC 和 PWM 在空闲模式下如果选择系统时钟可继续工作,并可唤醒系统)

0: 系统执行 SLEEP 指令时进入睡眠模式

#### RPAGE~RF-ISR(中断标志寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| _     | _    | _     | _     | T1IF  | EXIF  | ICIF  | TCIF  |

Bit0:TCIF-TCC 中断标志位

1:有中断

0: 无中断

注意:清除中断标志位时,必须使用 MOV RF, A 操作,不能使用 BTC 和 AND RF, A 指令操作。

#### IOPAGF~IOCF-IMR(WDT唤醒及中断使能控制寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| 0     | 0    | 0     | 0     | T1IE  | EXIE  | ICIE  | TCIE  |

Bit0:TCIE-TCC 中断使能控制

1:使能

0:禁止(默认)

# 3.4.2 TCC 定时设置说明

- 1、给 TCC 寄存器赋初始值;

- 2、设置 CONT 寄存器的值(选择作为计时器或计数器及预分频比):

- 3、作为计数器使用,需要在CONT寄存器选择TCC外部信号为正沿或负沿加1;

- 4、若需要执行中断功能,须设置 IOCF 寄存器中的 TCIE (Bit0) 为 1,并执行 EI 指令;

- 5、中断程序部分将手动保存 ACC、STATUS 及 R4 于堆栈器中,执行 RETI 指令后,再自堆栈中取出,退出中断前要清楚 TCC 中断标志位。

# 3.4.3 TCC 定时计算说明

TCC 定时功能通过写值到 TCC 寄存器,给定时器赋初始值,定时器从初始值位置开始累加,直至定时器溢出产生中断。

#### TCC 定时时间计算公式(选择内部指令周期时钟):

TCC 定时时间=(系统时钟分频/Fosc)\*(TCC 分频)\*(256-TCC 初始值) 举例:

系统时钟分频=2clock, Fosc=8 MHz, TCC 分频选择=4 分频, TCC 初始值=156;

TCC 定时时间= (2/8) \*(4)\*(256-156)=100us

#### TCC 定时时间计算公式(选择外部输入时钟):

TCC 定时时间=(外部输入时钟)\*(TCC 分频)\*(256-TCC 初始值) 举例:

外部输入时钟=1 MHz, TCC 分频选择=4 分频, TCC 初始值=156;

TCC 定时时间= (1) \*(4)\*(256-156)=400us

晶哲科技 改变从芯开始

第 30 页 共 54 页

# 3.5 工作模式

JZ8P1525 可以在 4 种工作模式下以不同的时钟频率工作,这些模式可以控制振荡器的工作、程序的执行以及模拟电路的功能损耗。

- 高速模式:系统时钟选择高速IRC时钟;

- 低速模式:系统时钟选择内部低速时钟;

- 空闲模式:系统时钟正常工作,其他部分进入睡眠(TCC和PWM选择系统时钟可继续工作 并可唤醒系统、RTC溢出与端口状态变化均可唤醒系统);

- 睡眠模式: 所有功能暂停工作,系统进入睡眠(RTC模式可工作),可端口状态变化唤醒、WDT溢出唤醒、RTC溢出唤醒、外部复位引脚输入唤醒;

| 功能模块   | 高速模式     | 低速模式     | 空闲模式                                     | 睡眠模式                        |

|--------|----------|----------|------------------------------------------|-----------------------------|

| IHRC   | 运行       | STPHX 控制 | STPHX 控制                                 | 停止                          |

| ILRC   | 运行       | 运行       | 运行                                       | 停止                          |

| CPU 指令 | 执行       | 执行       | 停止                                       | 停止                          |

| TCC    | 可工作      | 可工作      | 可工作                                      | 停止                          |

| PWM    | 可工作      | 可工作      | 可工作                                      | 停止                          |

| 内部中断   | 全部有效     | 全部有效     | TCC, PWM 有效                              | RTC 有效                      |

| 外部中断   | 有效       | 有效       | 无效                                       | 无效                          |

| 唤醒功能   | -        | -        | P6IC, TCC, PWM,<br>RTC, WDT,<br>外部 RESET | P6IC, RTC, WDT<br>,外部 RESET |

| 看门狗定时器 | WDT 选项控制 | WDT 选项控制 | WDT 选项控制                                 | WDT 选项控制                    |

# 3.5.1 高速模式

高速模式是系统高速时钟工作模式,系统时钟源由高速 RC 振荡器提供。程序被执行。上电复位或任意一种复位触发后,系统进入高速模式执行程序。当系统从睡眠模式被唤醒后进入高速模式。高速模式下,高速振荡器正常工作,功耗最大。

- 程序被执行,所有的功能都可控制;

- 系统速率为高速;

- 高速振荡器和内部低速振荡器都正常工作;

- 通过CPU模式控制寄存器,系统可以从高速模式切换到其它任何一种工作模式;

- 系统从睡眠模式唤醒后进入高速模式;

- 低速模式可以切换到高速模式;

- 从高速模式进入到空闲模式,唤醒后返回到高速模式;

晶哲科技 改变从芯开始

第 31 页 共 54 页

#### 3.5.2 低速模式

低速模式为系统低速时钟工作模式。系统时钟源由内部低速 RC 振荡器提供。低速模式由 CPU 模式控制寄存器的 CLKMD 位控制。当 CLKMD=0 时,系统为高速模式; 当 CLKMD=1 时,系统进入低速模式。进入低速模式后,不能自动禁止高速振荡器,必须通过 SPTHX 位来禁止以减少功耗。

- 程序被执行,所有的功能都可控制;

- 系统速率为低速;

- 内部低速RC振荡器正常工作,高速振荡器由STPHX=1控制。低速模式下,强烈建议停止高速振荡器;

- 通过CPU模式控制寄存器,低速模式可以切换进入其它的工作模式;

- 从低速模式进入到睡眠模式,唤醒后返回到低速模式;

- 高速模式可以切换到低速模式;

- 从低速模式进入到空闲模式,唤醒后返回到低速模式;

#### 3.5.3 空闲模式

空闲模式是另外的一种理想状态。在睡眠模式下,所有的功能和硬件设备都被禁止,但在空闲模式下,系统时钟保持工作,空闲模式下的功耗大于睡眠模式下的功耗。空闲模式下,不执行程序,但具有唤醒功能的定时器和 PWM 仍正常工作,定时器和 PWM 的时钟源为仍在工作的系统时钟。空闲模式下,有 4 种方式可以将系统唤醒: 1、P6 端口状态变化触发; 2、TCC定时器唤醒; 3、PWM 唤醒; 4、RTC定时唤醒。用户可以给定时器或者 PWM 设定固定的周期,系统就在溢出时被唤醒。由 CPU 模式控制寄存器 IDLE 位决定是否进入空闲模式,当 IDLE=1,系统进入空闲模式。

- 程序停止执行,所有的功能被禁止;

- 具有唤醒功能的定时器正常工作;

- 作为系统时钟源的振荡器正常工作,其它的振荡器工作状态取决于系统工作模式的配置;

- 由高速模式进入到空闲模式,被唤醒后返回到高速模式;

- 由低速模式进入到空闲模式,被唤醒后返回到低速模式;

- 空闲模式下的唤醒方式为P6端口状态变化触发唤醒、TCC定时器溢出和PWM周期溢出、RTC 定时唤醒:

- ● 空闲模式下TCC和PWM功能仍然有效;

# 3.5.4 睡眠模式

睡眠模式是系统的理想状态,不执行程序(RTC 除外),振荡器也停止工作。整个芯片的功耗低于 1uA。睡眠模式可以由 P6 端口状态变化触发唤醒、RTC 溢出唤醒、外部复位引脚输入、WDT 溢出。从高速模式或者低速模式进入睡眠模式,被唤醒后将返回到对应模式。由 CPU 模式控制寄存器的 IDLE 位控制是否进入睡眠模式,当 IDLE=0,系统进入睡眠模式。

- 程序停止执行,所有的功能被禁止;

- 所有的振荡器,包括外部高速振荡器、内部高速振荡器和内部低速振荡器都停止工作;

- 功耗低于1uA;

- 由高速模式进入到睡眠模式,被唤醒后返回到高速模式;

- 由低速模式进入到睡眠模式,被唤醒后返回到低速模式;

- 睡眠模式的唤醒源为P6端口状态变化触发、RTC溢出唤醒、外部复位引脚输入、WDT溢出;

# 3.6 睡眠唤醒功能模块

#### 3.6.1 睡眠唤醒方式说明

芯片执行"SLEEP"指令可以转到休眠模式(低功耗模式)。进入休眠模式时,系统时钟停止,所有模块停止工作,WDT(若使能)清0,但继续运行。

单片机可被如下情况唤醒:

- 1、WDT 复位唤醒;

- 2、外部复位引脚输入唤醒;

- 3、RTC唤醒;

- 4、端口状态改变唤醒;

后两种方式则保持了程序的延续性,可以通过程序选择继续原有的进程(SLEEP 前执行 DI)或执行相应的跳转(SLEEP 前执行 EI),并打开相应的使能控制位,跳转到中断向量的位置。

注意:清除中断标志位时,必须使用 MOV RF, A 操作,不能使用 BTC 和 AND RF, A 指令操作。

#### 3.6.2 相关寄存器说明

#### CONT (控制寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| RTCS  | INT  | TS    | TE    | PAB   | PSR2  | PSR1  | PSR0  |

Bit<7>:RTCS

当 RTC 在 OPTION 中关闭时,作为通用读写位;

当 RTC 在 OPTION 中使能时:

1:选择外部晶振时钟(LXT的4分频)

0:TCC 时钟由 TCCCKS 和 TS 决定, TCCCKS=1 时钟源选择 FOSC, TCCCKS=0 时钟源由 TS 决定 TCC 时钟源优先级 RTCS>TCCCKS>TS

#### RPAGE~RD-ICIECR(P6端口中断唤醒使能寄存器)

| Bit 7 | Bit6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------|------|---------|---------|---------|---------|---------|---------|

| 0     | 0    | P6WK<5> | P6WK<4> | P6WK<3> | P6WK<2> | P6WK<1> | P6WK<0> |

Bit<7:0>:P6WK<7:0>-P6 端口中断唤醒使能

1:使能

0:禁止(默认)

注意:在 OPTION 中端口唤醒设置选择中,如果选择 P6 端口非独立控制,则端口唤醒不受 RD 寄存器控制,否则需要对 RD 寄存器做处理,不然端口无法唤醒。

#### RPAGE~RE-CPUCON(CPU 模式控制寄存器)

| Bit 7 | Bit6   | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------|--------|-------|-------|-------|-------|-------|

| IPWM1 | PWMCKS | TCCCKS | PWMWE | TCCWE | STPHX | CLKMD | IDLE  |

Bit<6>:PWMCKS-PWM 时钟源

1:选择系统时钟

晶哲科技 改变从芯开始

第 34 页 共 54 页

0:选择指令周期时钟

Bit<5>:TCCCKS-TCC 时钟源选择

1:选择系统时钟

0:选择指令周期时钟

Bit<4>:PWMWE-PWM 唤醒

1:PWM 唤醒使能,可唤醒空闲模式

0:PWM 唤醒禁止

Bit<3>:TCCWE-TCC 唤醒

1:TCC 唤醒使能,可唤醒空闲模式,RTC 模式下可唤醒睡眠以及空闲模式

0:TCC 唤醒禁止

(RTC 模式下设置 TCCWE=1&RTCS=1 休眠时 LXT 继续工作不会停止,否则时休眠会停止 LXT)

Bit<2>:STPHX-高速时钟

1:停止高速时钟,包括 IRC 和晶振振荡器时钟(不包括 RTC 时钟)

0:高速时钟正常工作

Bit<1>:CLKMD-系统时钟

1: 系统时钟使用低速 RC 振荡器时钟

0: 系统时钟使用高速 IRC 或者晶振振荡器时钟

(系统从正常模式进入低速模式时 先设置 CLKMD=1,后设置 STPHX=1,系统从低速模式进入正常模式时 先设置 STPHX=0,后设置 CLKMD=0)

Bit<0>:IDLE-空闲模式

1: 系统执行 SLEEP 指令时进入空闲模式,系统时钟正常工作

(TCC 和 PWM 在空闲模式下如果选择系统时钟可继续工作,并可唤醒系统)

0:系统执行 SLEEP 指令时进入睡眠模式

#### RPAGE~RF-ISR(中断标志寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| 0     | 0    | 0     | 0     | T1IF  | EXIF  | ICIF  | TCIF  |

Bit1:ICIF-P6 端口输入状态改变中断标志位

1:有中断

0: 无中断

#### IOPAGE~IOCE-WDTCR(看门狗控制寄存器)

| Bit 7 | Bit6 | Bit 5    | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

|-------|------|----------|----------|----------|-------|-------|-------|

| WDTEN | EIS  | P6WDS<5> | P6WDS<4> | P6WDS<3> | PWM3S | PWM2S | PWM1S |

Bit<7>:WDTEN-WDT 使能控制位

1:使能

0:禁止

晶哲科技 改变从芯开始

第 35 页 共 54 页

#### IOPAGF~IOCF-IMR(WDT 唤醒及中断使能控制寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| 0     | 0    | 0     | 0     | T1IE  | EXIE  | ICIE  | TCIE  |

Bit<1>:P6ICIE-P6端口状态改变中断使能控制

1:使能

0:禁止(默认)

# 3.6.3 端口状态改变查询方式唤醒设置

- 1、PORT6 端口唤醒口设为输入;

- 2、可以根据需要选择唤醒口的内部上拉或下拉;

- 3、使能 PORT 端口状态改变中断;

- 4、使能端口状态改变独立中断及唤醒控制;

- 5、执行 DI 指令,不进入中断地址口;

- 6、执行"SLEEP"指令,进入睡眠 SLEEP 模式;

- 7、唤醒后, 执行 SLEEP 的下一条指令。

# 3.6.4 端口状态改变中断方式唤醒设置

- 1、PORT6 端口唤醒口设为输入;

- 2、可以根据需要选择唤醒口的内部上下拉;

- 3、使能端口状态改变独立中断及唤醒控制;

- 4、使能 PORT 端口状态改变中断;

- 5、执行"EI"指令,等待进入中断地址口;

- 6、下指令"SLEEP", 进入睡眠 SLEEP 模式;

- 7、唤醒后会进入中断地址口,退出中断后,执行 SLEEP 下一条指令。

# 3.6.5 重要说明

- 1. P6 口睡眠前不再需要 MOV P6, P6 操作可直接唤醒;

- 2. 所有唤醒不再需要设置 WDT 硬件使能和软件使能,唤醒后不再需要关闭软件使能,也不再需要设置分频器给 WDT;

#### ◆ TCC RTC 唤醒

- 配置选择使能 RTC 功能:

- CONT 寄存器的 RTCS=1, TCC 时钟自动选择 LXT;

- CPUCON 寄存器的 TCCWE=1(不需要中断的时候不需要设置 TCIE=1);

晶哲科技 改变从芯开始

第 36 页 共 54 页

#### ◆ TCC 正常下唤醒 IDLE

- CPUCON 寄存器的 IDLE=1, TCCWE=1, TCCCKS=1(不需要中断的时候不需要设置 TCIE=1);

- 执行 SLEEP 指令;

#### ◆ TCC 低速模式下唤醒 IDLE

- CPUCON 寄存器的 IDLE=1, TCCWE=1, TCCCKS=1, CLKMD=1, STPHX=1(不需要中断的时候不需要设置 TCIE=1);

- 执行 SLEEP 指令;

#### ◆ T1 正常下唤醒 IDLE

- PWMCON 寄存器 T1EN=1;

- 设置周期寄存器 PRD;

- CPUCON 寄存器的 IDLE=1, PWMWE=1, PWMCKS=1(不需要中断的时候不需要设置T1IE=1);

- 执行 SLEEP 指令;

#### ◆ T1 低速模式下唤醒 IDLE

- PWMCON 寄存器 T1EN=1;

- 设置周期寄存器 PRD;

- CPUCON 寄存器的 IDLE=1, PWMWE=1, PWMCKS=1, CLKMD=1, STPHX=1(不需要中断的时候不需要设置 T1IE=1);

- 执行 SLEEP 指令;

## 3.7 PWM 脉宽调制功能模块

JZ8P1525 提供 3 路共周期的 8Bit PWM 信号。PWM 输出波形由周期及占空因数决定,传输速率为周期倒数。

PWM 带有周期溢出中断, 使能后可跳转到中断。

在 IDLE (空闲模式)下, PWM 在 CPU 模式控制寄存器中选择 PWMCKS=1 并且使能 PWMWE, 可唤醒系统。

## 3.7.1 PWM 脉宽调制寄存器说明

RPAGE~R8-PWMCON(PWM 控制寄存器)

| Bit 7 | Bit6   | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1      | Bit 0 |

|-------|--------|--------|--------|--------|-------|------------|-------|

| T1EN  | PWM3EN | PWM2EN | PWM1EN | T1PTEN |       | T1PSR<2:0> |       |

Bit<7>:T1EN-T1/PWM 计数器使能

1:使能

0:禁止

Bit<6>:PWM3EN-PWM3 输出使能控制位

1:使能 (P60 输出 PWM3)

0:禁止

Bit<5>:PWM2EN-PWM2 输出使能控制位

1:使能 (P61 输出 PWM2)

0:禁止

Bit<4>:PWM1EN-PWM1 输出使能控制位

1:使能 (P62 输出 PWM1)

0:禁止

Bit<3:0>:T1PTEN PT1P<2:0>-T1 预分频选择控制位

| T1PTEN | T1PSR<2> | T1PSR<1> | T1PSR<0> | T1 分频比 |

|--------|----------|----------|----------|--------|

| 0      | 0        | 0        | 0        | 1:1    |

| 1      | 0        | 0        | 0        | 1:2    |

| 1      | 0        | 0        | 1        | 1:4    |

| 1      | 0        | 1        | 0        | 1:8    |

| 1      | 0        | 1        | 1        | 1:16   |

| 1      | 1        | 0        | 0        | 1:32   |

| 1      | 1        | 0        | 1        | 1:64   |

| 1      | 1        | 1        | 0        | 1:128  |

| 1      | 1        | 1        | 1        | 1:256  |

#### RPAGE~R9-PRD (PWM 周期寄存器)

Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | PRD<7:0>

T1/PWM 周期寄存器

### RPAGE~RA-PDC1 (PWM1 占空比寄存器)

Bit 7 Bit6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PDC1<7:0>

Bit<7:0>:PDC1<7:0>-PWM1 占空比

### RPAGE~RB-PDC2(PWM2 占空比寄存器)

Bit 7 Bit6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PDC2<7:0>

Bit<7:0>:PDC2<7:0>-PWM2 占空比

### RPAGE~RC-PDC3(PWM3 占空比寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

|       |      |       | PDC3  | <7:0> |       |       |       |

Bit<7:0>:PDC3<7:0>-PWM3 占空比

#### RPAGE~RE-CPUCON(CPU 模式控制寄存器)

| Bit 7 | Bit6   | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------|--------|-------|-------|-------|-------|-------|

| IPWM1 | PWMCKS | TCCCKS | PWMWE | TCCWE | STPHX | CLKMD | IDLE  |

Bit<7>: IPWM1-PWM 互补输出

1:PWM1 输出取反

0:PWM1 输出无取反

Bit<6>: PWMCKS-PWM 时钟源

1:选择系统时钟

0:选择指令周期时钟

Bit<4>:PWMWE-PWM 唤醒

1:PWM 唤醒使能,可唤醒空闲模式

0:PWM 唤醒禁止

### RPAGE~RF-ISR(中断标志寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| 0     | 0    | 0     | 0     | T1IF  | EXIF  | ICIF  | TCIF  |

Bit<3>:T1IF-T1/PWM 周期中断标志位,T1/PWM 周期置 1,软件清 0

注意:清除中断标志位时,必须使用 MOV RF, A 操作,不能使用 BTC 和 AND RF, A 指令操作。

### IOPAGE~IOCE-WDTCR(看门狗控制寄存器)

| Bit 7 | Bit6 | Bit 5    | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

|-------|------|----------|----------|----------|-------|-------|-------|

| WDTEN | EIS  | P6WDS<5> | P6WDS<4> | P6WDS<3> | PWM3S | PWM2S | PWM1S |

晶哲科技 改变从芯开始

第 39 页 共 54 页

Bit<2>:PWM3S-PWM3 输出脚位映射选择位

1:PWM3 映射至 P65 口

0:PWM3 映射至 P60 口

Bit<1>:PWM2S-PWM2 输出脚位映射选择位

1:PWM2 映射至 P64 口

0:PWM2 映射至 P61 口

Bit<0>:PWM1S-PWM1输出脚位映射选择位

1:PWM1 映射至 P63 口

0:PWM1 映射至 P62 口

### IOPAGF~IOCF-IMR(WDT 唤醒及中断使能控制寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| 0     | 0    | 0     | 0     | T1IE  | EXIE  | ICIE  | TCIE  |

Bit<3>:T1IE-T1 中断使能位

1:使能

0:禁止(默认)

### 3.7.2 PWM 脉宽调制设置说明

- 1、设置 PWMCON 寄存器,选择相应的定时器为 PWM 模式、定时器的分频比、定时器中断类型(若使能 PWM 中断)、定时器的时钟源等;

- 2、写 RPAGE-R9 寄存器的值,确定该 PWM 通道的周期;

- 3、写 PDCX 寄存器的值,确定该 PWM 通道的占空比;

- 4、使能相应定时器;

- 5、使能或禁止 PWM 对应的定时器中断,并下"EI"或"DI"指令(如果需要)。

## 3.7.3 PWM 计算说明

PWM 提供一个带 8bit 可编程预分频的时钟计数器(T1),作为 PWM 模块的波特率时钟发生器。可通过使能 PWM 控制寄存器中的 T1EN,使能 T1 计数器功能,通过 T1PTEN 及 T1PSR<2:0> 控制位,可进行 T1 计数器的预分频设置。

PWM 周期通过写值到 PWM 周期寄存器 (PRD),当 T1 计数器的值与 PRD 值相等,在下一个递增周期发生如下事件:

T1 计数器清零;

对应 PWM 输出引脚置高电平;

产生 PWM 周期溢出中断 (若使能);

PWM 占空比由 PDC1/PDC2/PDC3 锁存到 PDC/T1 比较寄存器;

晶哲科技 改变从芯开始

第 40 页 共 54 页

PWM 周期计算公式:Perid=PRD\*(1/fosc)\*CLOCKS\*T1 预分频比(PWM 时钟源为指令周期时钟)PWM 周期计算公式:Perid=PRD\*(1/fosc)\*T1 预分频比(PWM 时钟源为系统时钟)PWM 占空比计算公式:Duty=PDCX\*(1/fosc)\*CLOCKS\*T1 预分频比(PWM 时钟源为指令周期时钟)PWM 占空比计算公式:Duty=PDCX\*(1/fosc)\*T1 预分频比(PWM 时钟源为系统时钟)其中 PRD 为 PWM 周期值,fosc 为时钟源频率,CLOCKS 为时钟分频,PDCX 为 PWM 占空比

### 举例 1: PWM1 输出周期为 100us, 占空比为 50us 的波形 (PWM 时钟源为指令周期时钟)

CPUCON&=Oxbf; //PWM 时钟源选择指令周期时钟

PWMCON=0x99; //使能 PWM1 且 T1 分频设置为 4 分频, IRC 选择 8M, 2Clocks

PRD=100; //周期 Perid=100\*(1/8)\*2\*4=100us

DT1=50; //占空比 Duty=50\*(1/8)\*2\*4=50us

#### 举例 2: PWM1 输出周期为 100us, 占空比为 50us 的波形 (PWM 时钟源为系统时钟)

CPUCON =0x40; //PWM 时钟源选择系统时钟

PWMCON=0x99; //使能 PWM1 且 T1 分频设置为 4 分频, IRC 选择 8M, 2Clocks

PRD=200; //周期 Perid=200\*(1/8)\*4=100us DT1=100; //占空比 Duty=100\*(1/8)\*4=50us

# 3.8 中断功能模块

JZ8P1525 具有 4 个中断源,无论是使用其中哪一个中断, 都必须使总中断使能, 即"EI"指令。中断向量为固定默认地址 008H. 下面分别是每个中断的特性:

|    | 中断源         | 使能条件          | 中断标志 | 中断向量 |

|----|-------------|---------------|------|------|

| 外部 | 外部中断        | EI + EXIE = 1 | EXIF | 008H |

| 外部 | 端口输入改变      | EI + ICIE = 1 | ICIF | 008Н |

| 内部 | TCC 溢出中断    | EI + TCIE = 1 | TCIF | 008Н |

| 内部 | T1/PWM 周期中断 | EI + T1IE = 1 | T1IF | 008H |

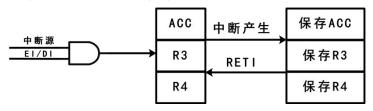

RPAGE~RF 为中断状态标志寄存器,它们记录了当某个中断产生中断请求后的中断标志位。IOPAGF~IOCF 为中断设置寄存器,中断的允许与禁止在这两个寄存器中设置。总中断的允许是通过下"EI"指令,相反,总中断的禁止是通过下"DI"指令。当一个中断产生时,它的下一条指令的执行将从它们特定的地址处执行。在离开中断服务程序之前相应的中断标志位必须清零,这样才能避免中断的误动作。

当执行中断子程序时,强烈建议在程序中使用中断保护,将 ACC、R3、R4 的内容保存起来,直到离开中断子程序后,需要手动将被保留的值载入 ACC、R3、R4,如此是为了避免在执行中断子程序时,有将 ACC、R3、R4 的值改变,导致回主程序时发生错误。如下图所示:

## 3.8.1 中断寄存器说明

RPAGE~RF-ISR(中断标志寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| _     | _    | _     | -     | T1IF  | EXIF  | ICIF  | TCIF  |

Bit<3>:T1IF-T1/PWM 周期中断标志位,软件清 0

Bit<2>:EXIF-外部端口中断标志位(由 EXINT 引脚上升沿或者下降沿置 1, 软件清 0)

Bit<1>: ICIF-P6 端口状态改变中断标志位,软件清 0

Bit<0>:TCIF-TCC 中断标志位, 软件清 0

1:有中断

0: 无中断

注意:清除中断标志位时,必须使用 MOV RF,A 操作,不能使用 BTC 和 AND RF,A 指令操作。

#### IOPAGF~IOCF-IMR(中断使能控制寄存器)

| Bit 7 | Bit6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|------|-------|-------|-------|-------|-------|-------|

| 0     | 0    | 0     | 0     | T1IE  | EXIE  | ICIE  | TCIE  |

Bit<3>:T1IE-T1 中断使能位

晶哲科技 改变从芯开始

第 42 页 共 54 页

Bit<2>:EXIE-外部中断使能控制

Bit<1>:ICIE-P6端口状态改变中断使能控制

Bit<0>:TCIE-TCC 溢出中断使能控制

1:使能

0:禁止(默认)

## 3.9 复位功能模块

JZ8P1525 系统提供 4 种复位方式:

POR 上电复位

RESET 脚输入低电平复位

WDT 看门狗溢出复位

LVR 低电压复位

以上任意一种复位发生时,所有的系统寄存器初始化到复位值,程序停止运行,同时程序计数器 PC 清零。复位结束后,系统从向量 0000H 处重新开始运行。

任何一种复位情况都需要一定的响应时间,系统复位机制能够保证 MCU 的可靠复位。不同类型的振荡器,完成复位所需要的时间也不同。因此,VDD 的上升速度和不同振荡器的起振时间都是不固定的。RC 振荡器的起振时间最短,晶体振荡器的起振时间则较长。在用户终端使用的过程中,应注意考虑应用场景对上电复位时间的要求。

## 3.9.1 WDT 看门狗复位

看门狗复位是系统的一种保护设置。在正常状态下,由程序将看门狗定时器清零。若出错,系统处于未知状态,看门狗定时器溢出,此时系统复位。看门狗复位后,系统重启进入 正常状态。

- 看门狗定时器状态:系统检测看门狗定时器是否溢出,若溢出,则系统复位:

- 系统初始化: 所有的系统寄存器被置为初始化默认值;

- 振荡器开始工作:振荡器开始提供系统时钟;

- 执行程序:上电结束,程序开始运行;

#### 看门狗定时器应用注意事项:

- 对看门狗清零之前,检查 I/O 口的状态和 RAM 的内容可增强程序的可靠性;

- 不能在中断中对看门狗清零,否则无法侦测到主程序跑飞的状况;

- ◆ 程序中应该只在主程序中有一次清看门狗的动作,这种架构能够最大限度的发挥看门 狗的保护功能。

## 3.9.2 POR 上电复位

上电复位与 LVR 操作密切相关。系统上电的过程呈逐渐上升的曲线形式,需要一定时间才能达到正常电平值。

- 上电:系统检测到电源电压上升并等待其稳定;

- 外部复位(仅限于外部复位引脚使能状态):系统检测外部复位引脚状态。如果不为 高电平,系统保持复位状态直到外部复位引脚释放:

- 系统初始化: 所有的系统寄存器被置为初始值;

- 振荡器开始工作:振荡器开始提供系统时钟;

晶哲科技 改变从芯开始

第 44 页 共 54 页

● 执行程序:上电结束,程序开始运行;

上电复位时间由 OPTION 中的【复位时间】选择决定,如下表所示:

| PWRT 与 WDT | 复位建立时间            |

|------------|-------------------|

| PWRT=WDT   | 4.5ms(跟随看门狗复位时间)  |

| PWRT=WDT   | 18ms(跟随看门狗复位时间)   |

| PWRT=WDT   | 72ms(跟随看门狗复位时间)   |

| PWRT=WDT   | 288ms (跟随看门狗复位时间) |

| PWRT≠WDT   | 140us (独立固定复位时间)  |

## 3.9.3 LVR 低电压复位

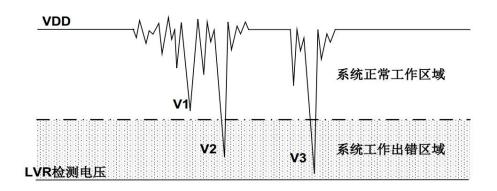

掉电复位针对外部因素引起的系统电压跌落情形 (例如,干扰或外部负载的变化),掉 电可能会引起系统工作状态不正常或程序执行错误。

电压跌落可能会进入系统死区。系统死区意味着电源不能满足系统的最小工作电压要求。 上图是一个典型的掉电复位示意图。图中,VDD 受到严重的干扰,电压值降的非常低。虚线 以上区域系统正常工作,在虚线以下的区域内,系统进入未知的工作状态,这个区域称作死 区。当 VDD 跌至 V1 时,系统仍处于正常状态; 当 VDD 跌至 V2 和 V3 时,系统进入死区,则容易导致出错。以下情况系统可能进入死区:

#### DC 运用中:

DC 运用中一般都采用电池供电,当电池电压过低或单片机驱动负载时,系统电压可能跌落并进入死区。这时,电源不会进一步下降到 LVR 检测电压,因此系统维持在死区。

#### AC 运用中:

系统采用 AC 供电时,DC 电压值受 AC 电源中的噪声影响。当外部负载过高,如驱动马达时,负载动作产生的干扰也影响到 DC 电源。VDD 若由于受到干扰而跌落至最低工作电压以下时,则系统将有可能进入不稳定工作状态。在 AC 运用中,系统上、下电时间都较长。其中,

晶哲科技 改变从芯开始

第 45 页 共 54 页

上电时序保护使得系统正常上电,但下电过程却和 DC 运用中情形类似,AC 电源关断后,VDD 电压在缓慢下降的过程中易进入死区。

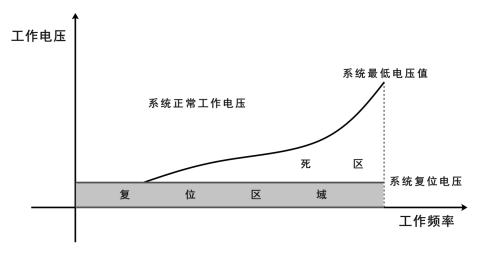

## 3.9.4 工作频率与 LVR 低压检测关系

为了改善系统掉电复位的性能,首先必须明确系统具有的最低工作电压值。系统最低工作电压与系统执行速度有关,不同的执行速度下最低工作电压值也不同。

如上图所示,系统正常工作电压区域一般高于系统复位电压,同时复位电压由低电压检测(LVR)电平决定。当系统执行速度提高时,系统最低工作电压也相应提高,但由于系统复位电压是固定的,因此在系统最低工作电压与系统复位电压之间就会出现一个电压区域,系统不能正常工作,也不会复位,这个区域即为死区。

为避免出现死区电压,在选择工作频率的时候,要选择相应的 LVR 复位电压点。如下表:

| 工作频率               | LVR 复位电压点 |

|--------------------|-----------|

| IRC-8M, 2Clock     | LVR=2.4V  |

| IRC-8M, 4Clock     | LVR=1.8V  |

| IRC-8M, 8Clock     | LVR=1.8V  |

| IRC-1M, 2Clock     | LVR=1.8V  |

| IRC-910KHz, 2Clock | LVR=1.8V  |

注:此工作频率和 LVR 复位电压点的对应值,只是推荐值,用户在使用过程中,根据用于的具体应用场合可以适当的调整复位电压点。

## 3.9.5 寄存器上电复位值

| 地址  | 名称        | 复位值       | 地址  | 名称   | 复位值       |

|-----|-----------|-----------|-----|------|-----------|

| 0x0 | RO/IAR    | _         | 0x0 | _    | _         |

| 0x1 | R1/TCC    | 0000 0000 | 0x1 | CONT | 0011 1111 |

| 0x2 | R2/PCL    | 0000 0000 | 0x2 | _    | _         |

| 0x3 | R3/STATUS | 0001 1uuu | 0x3 | _    | -         |

| 0x4 | R4/RSR    | 11uu uuuu | 0x4 | _    | _         |

晶哲科技 改变从芯开始

第 46 页 共 54 页

| 0x5  | _         | _         | 0x5 | _           | _         |

|------|-----------|-----------|-----|-------------|-----------|

| 0x6  | R6/PORT6  | 0011 1111 | 0x6 | IOC6/P6CR   | 1111 1111 |

| 0x7  | _         | _         | 0x7 | IOC7/HDSOCR | 0000 0000 |

| 0x8  | R8/PWMCON | 0000 0000 | 0x8 | IOC8/HDS1CR | 0000 0000 |

| 0x9  | R9/PRD    | 0000 0000 | 0x9 | IOC9/PHDCR  | 1111 1111 |

| OxA  | RA/PDC1   | 0000 0000 | OxA | IOCA/HDS2CR | 0000 0000 |

| 0xB  | RB/PDC2   | 0000 0000 | 0xB | IOCB/PDCR   | 1111 1111 |

| 0xC  | RC/PDC3   | 0000 0000 | 0xC | IOCC/ODCR   | 1111 1111 |

| 0xD  | RD/ICIECR | 0000 0000 | 0xD | IOCD/PHCR   | 1111 1111 |

| OxE  | RE/CPUCON | 0000 0000 | 0xE | IOCE/WDTCR  | 1000 0000 |

| 0xF  | RF/ISR    | 0000 0000 | 0xF | IOCF/IMR    | 0000 0000 |

| 0x10 | 通用寄存器     | uuuu uuuu |     |             |           |

| ~    |           |           |     |             |           |

| 0x3f |           |           |     |             |           |

U=表示未知状态;

# 3.10 系统时钟功能模块

JZ8P1525 内部集成了3种振荡器,可以通过 option 实现配置。具体参看下表:

| 振荡器类型          | 说明                     |

|----------------|------------------------|

| IRC(内置 RC 振荡器) | 可以通过 RCM 选择 910K/1M/8M |

| LXT (低速晶振)     | 32. 768K∼400K          |

| HXT (高速晶振)     | 400K~16M               |

说明:HXT 和 LXT 之间的系统频率过度点在 400KHz 左右。

### 3.10.1 内部 RC 振荡器模式 (IRC)

JZ8P1525 提供内部 RC 模式, 频率可选 910 KHz, 1MHz, 8MHz。通过设置 OPTION 的配置位,可选择 IRC 工作频率,下面是它们的对应关系:

| Firc    | IRC 频率          |

|---------|-----------------|

| 8 M     | IRC 频率选为 8MHz   |

| 1 M     | IRC 频率选为 1MHz   |

| 910 KHz | IRC 频率选为 910KHz |

JZ8P1525 提供了多种分频选择,可以在 OPTION 中选择,适用于更多的场合。如下表:

| Clocks  | Clocks 分频   |

|---------|-------------|

| 2clock  | 分频为 2clock  |

| 4clock  | 分频为 4clock  |

| 8clock  | 分频为 8clock  |

| 16clock | 分频为 16clock |

| 32clock | 分频为 32clock |

## 3.10.2 外部晶体振荡器/陶瓷谐振器 (XT)

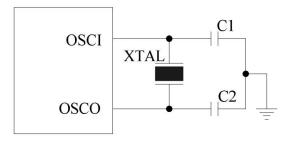

在大多数应用中,引脚 OSCO 和 OSCI 上可接晶体或陶瓷谐振器来产生振荡,电路图如下,不论是 HXT 还是 LXT 模式都适用,表中为 C1、C2 的推荐值。由于各个谐振器特性不同,用户应参参照其规格选择 C1、C2 的合适值。

晶体/振荡器电路

晶体振荡器或陶瓷振荡器的电容选择参考:

| 振荡器模式 | 频率模式 | 频率         | C1 (pF) | C2 (pF) |

|-------|------|------------|---------|---------|

| 陶瓷振荡器 | НХТ  | 455KHz     | 100-200 | 100-200 |

|       | LXT  | 32.768 KHz | 5-40    | 5-40    |

| 晶体振荡器 | ΠVT  | 1 MHz      | 5-30    | 5-30    |

|       | НХТ  | 4 MHz      | 5-30    | 5-30    |

注:以上数据仅供参考,一切以实物测试为准。

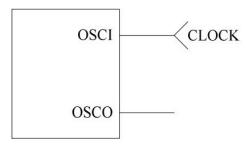

JZ8P1525 还可被 OSCI 引脚上的外部时钟信号驱动, 其应用图如下:

外部时钟示意图

## 3.10.3 时钟模块应用说明

内部振荡器是最常用的振荡模式,该模式可以省去外接的电路;

在使用外打时钟输入时,时钟信号要从 OSCI 输入, OSCO 可以悬空;

使用外部振荡器并且大于 400kHz 时一定要在烧写程序时的 OPTION 选项中选外部高速振荡器,小于 400kHz 时选外部低速振荡器:

外界条件不同,各振荡模式的时钟频率可能会有轻微差别,使用时应根据需要合理选择。 JZ8P1525 可提供 14pf, 18pf 和 25pf 3 种容值的内置电容,可在烧录 option 中进行选择。

# 4 CODE OPTION 寄存器

| CODE OPTION  | 选项        | 功能描述             |

|--------------|-----------|------------------|

| 毛门Xh         | 使能        | 看门狗 WDT 使能       |

| 看门狗 <b>-</b> | 禁止        | 看门狗 WDT 禁止       |

|              | 2 Clocks  | 指令周期选择 2 Clocks  |

|              | 4 Clocks  | 指令周期选择 4 Clocks  |

| Clocks 分频    | 8 Clocks  | 指令周期选择 8 Clocks  |

|              | 16 Clocks | 指令周期选择 16 Clocks |

|              | 32 Clocks | 指令周期选择 32 Clocks |

|              | IRC 模式    | 选择内部 RC 振荡方式     |

| 振荡方式         | HXT 模式    | 选择高速晶振振荡方式       |

|              | LXT 模式    | 选择低速晶振振荡方式       |

|              | 8M        | IRC 频率选择 8M      |

| IRC 频率       | 1M        | IRC 频率选择 1M      |

|              | 910KHz    | IRC 频率选择 910KHz  |

| 振荡器倍频        | 使能        | 使能振荡器倍频功能        |

| 选项           | 禁止        | 禁止振荡器倍频功能        |

|              | LVR=1.2V  | 低压复位点选择 1.2V     |

|              | LVR=1.6V  | 低压复位点选择 1.6V     |

|              | LVR=1.8V  | 低压复位点选择 1.8V     |

| <br>  复位电压   | LVR=2.4V  | 低压复位点选择 2.3V     |

|              | LVR=2.7V  | 低压复位点选择 2.5V     |

|              | LVR=3.1V  | 低压复位点选择 2.9V     |

|              | LVR=3.3V  | 低压复位点选择 3.1V     |

|              | LVR=3.6V  | 低压复位点选择 3. 3V    |

| <br>  代码加密   | 使能        | 烧录模式数据加密         |

|              | 禁止        | 烧录模式数据不加密        |

| 有益總口上茲       | 使能        | 使能 P63 端口上拉      |

| 复位端口上拉-      | 禁止        | 禁止 P63 端口上拉      |

| P63 端口 -     | GPIO      | P63 作为通用 I/0 口   |

| 「100 畑口      | GPI       | P63 作为输入口        |

|                        | RST                   | P63 作为外部复位端口                      |

|------------------------|-----------------------|-----------------------------------|

|                        | PWRT=WDT=4.5ms        | 唤醒建立时间=WDT 溢出时间(不分频)= 4.5ms       |

|                        | PWRT=WDT=18ms         | 唤醒建立时间=WDT 溢出时间(不分频)= 18ms        |

|                        | PWRT=WDT=72ms         | 唤醒建立时间=WDT 溢出时间(不分频)= 72ms        |

| 有户时间                   | PWRT=WDT=288ms        | 唤醒建立时间=WDT 溢出时间(不分频)= 288ms       |

| 复位时间                   | PWRT=140us, WDT=4.5ms | 唤醒建立时间=140us, WDT 溢出时间(不分频)=4.5ms |

|                        | PWRT=140us, WDT=18ms  | 唤醒建立时间=140us, WDT 溢出时间(不分频)=18ms  |

|                        | PWRT=140us, WDT=72ms  | 唤醒建立时间=140us, WDT 溢出时间(不分频)=72ms  |

|                        | PWRT=140us, WDT=288ms | 唤醒建立时间=140us, WDT 溢出时间(不分频)=288ms |

| <b>木</b> 丰世田           | 1/4K                  | 可以在程序空间前 1/4K 查表                  |

| 查表范围                   | 1K                    | 可以在程序空间 1K 内查表                    |

|                        | EMT                   | 端口输入特性为施密特 EMT 特性 (详细介绍见 3.3)     |

| <u>&gt;ш — ит ы</u> и. | SMT                   | 端口输入特性为施密特 SMT 特性 (详细介绍见 3.3)     |

| 端口特性                   | HSMT                  | 端口输入特性为施密特 HSMT 特性(详细介绍见 3.3)     |

|                        | INV                   | 端口输入特性为反相器 INV 特性(详细介绍见 3.3)      |

| D.C. 沙山 口 n.A. 亚日      | 独立控制                  | P6 端口独立控制唤醒(需设置 0x0D 寄存器)         |

| P6 端口唤醒                | 非独立控制                 | P6 端口非独立控制唤醒                      |

| RTC                    | 禁止                    | 双时钟功能禁止                           |

| RIC                    | 使能                    | 双时钟功能使能                           |

| P6 上下拉控制               | 屏蔽                    | 屏蔽 P65-P63 下拉                     |

| 10 工 1.4水1工帥1          | 使能                    | 使能 P65-P63 下拉, P63 上拉, 软件可控制      |

| 外部中断沿                  | EXINT 上升沿触发           | 外部中断脚上升沿触发                        |

| 选择                     | EXINT 下降沿触发           | 外部中断脚下降沿触发                        |

|                        | 内置电容关闭                | 晶振脚内置电容关闭                         |

| 晶振脚                    | 内置电容 7pf              | 晶振脚内置电容 14pf                      |

| 内置电容选择                 | 内置电容 9pf              | 晶振脚内置电容 18pf                      |

| (RTC 使能)               | 内置电容 12.5pf           | 晶振脚内置电容 25pf                      |

| 休眠唤醒                   | 兼容老 153 系列            | 兼容原 153 系列唤醒                      |

| 设置                     | 休眠时允许多种唤醒源<br>同时唤醒    | 可判断唤醒源类别                          |

| POWER                  | HIGH                  | 供电电压 5V 或者接近 5V 时选 HIGH           |

| 1 OHLIK                | LOW                   | 供电电压 3. 3V 或者接近 3. 3V 时选 LOW      |

# 5 芯片电气特性

# 5.1 芯片极限参数

| 工作温度(℃):   | ( √ ) E:-40-85;                 |

|------------|---------------------------------|

| 存储温度(℃):   | ( √ ) −65∼+150;                 |

| 极限电压(V)    | ( √ ) 其它0.3~6;_                 |

| 极限输入电压 (V) | ( √ )其它 <u>GND-0.3~VDD+0.5;</u> |

| 极限输出电压(V)  | ( √ )其它 GND-0.3~VDD+0.5;        |

# 5.2 芯片直流参数

(T=25℃, VDD=5V,数据仅供参考,以实际样机测试为准)

| 符号   | 参数说明                            | 条件                      | 最小       | 典型   | 最大       | 单位  |

|------|---------------------------------|-------------------------|----------|------|----------|-----|

| IRC1 | IRC1 (校正后)                      | OPTION 选择 8MHz          | _        | 8    | _        | MHz |

| IRC2 | IRC2 (校正后)                      | OPTION 选择 1MHz          | _        | 1    | _        | MHz |

| IOH1 | 输出高电平驱动(P60/61/62)              | Ioh=4.4V                | 14       | 15   | 16       | mA  |

| IOH2 | 输出高电平驱动 (P63)                   | Ioh=4.4V                | 5        | 6    | 7        | mA  |

| I0H3 | 输出高电平驱动(P64/65)                 | Ioh=4.4V                | 10       | 11   | 12       | mA  |

| IOH4 | 输出高电平驱动增强<br>(P60/61/62 选择最大档位) | Ioh=4.4V                | 115      | 120  | 125      | mA  |

| IOH5 | 输出高电平驱动增强 (P63)                 | Ioh=4.4V                | 10       | 11   | 12       | mA  |

| IOH6 | 输出高电平驱动增强(P64/65)               | Ioh=4.4V                | 16       | 17   | 18       | mA  |

| IOL1 | 输出低电平驱动(P60/61/62)              | Io1=0.6V                | 20       | 21   | 22       | mA  |

| IOL2 | 输出低电平驱动(P63/64/65)              | Io1=0.6V                | 15       | 17   | 19       | mA  |

| IOL3 | 输出低电平驱动增强<br>(P60/61/62 选择最大档位) | Io1=0.6V                | 110      | 115  | 120      | mA  |

| IOL4 | 输出低电平驱动增强<br>(P63/64/65)        | Io1=0.6V                | 25       | 28   | 30       | mA  |

| IOH7 | 输出高电平弱驱动(P63/64/65)             | Ioh=4.4V                | 1.0      | 1.1  | 1.2      | mA  |

| IOL5 | 输出低电平弱驱动 (P63/64/65)            | Io1=0.6V                | 4        | 5    | 7        | mA  |

| IPH  | 上拉电流                            | 上拉使能,输入接地               | 90       | 100  | 110      | μД  |

| IPD  | 下拉电流                            | 下拉使能,输入接 VDD            | 45       | 50   | 55       | μД  |

| Isb1 | 关机电流 1                          | 输入接 VDD,输出悬空,<br>WDT 禁用 | -        | -    | 1        | μД  |

| Isb2 | 关机电流 2                          | 输入接 VDD,输出悬空,           | _        | -    | 12       | μД  |

| Iop2 | 工作电流 1 (VDD=5V)                 | IRC=8MHz 2clock         | _        | 1.2  | 1.5      | mA  |

| Iop2 | 工作电流 2 (VDD=5V)                 | IRC=1MHz 2clock         | -        | 0.2  | 0.3      | mA  |

| LVR  | 低电压复位电压                         | 选择 LVR 复位点              | V1vr-0.2 | V1vr | V1vr+0.2 | V   |

# 6 封装尺寸信息

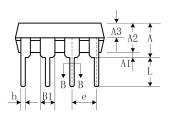

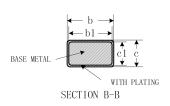

# 6.1 8PIN 封装尺寸

| CVMDOI | M    | IILLIMETE | ER   |

|--------|------|-----------|------|

| SYMBOL | MIN  | NOM       | MAX  |

| A      | 3.60 | 3.80      | 4.00 |

| A1     | 0.51 | _         | 1    |

| A2     | 3.10 | 3.30      | 3.50 |

| A3     | 1.50 | 1.60      | 1.70 |

| b      | 0.44 | -         | 0.53 |

| b1     | 0.43 | 0.46      | 0.48 |

| B1     |      | 1.52BSC   |      |

| С      | 0.25 | -         | 0.31 |

| c1     | 0.24 | 0.25      | 0.26 |

| D      | 9.05 | 9.25      | 9.45 |

| E1     | 6.15 | 6.35      | 6.55 |

| е      |      | 2.54BSC   |      |

| eA     |      | 7.62BSC   |      |

| eВ     | 7.62 | _         | 9.50 |

| еC     | 0    | _         | 0.94 |

| L      | 3.00 | -         | _    |

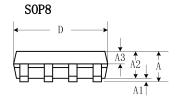

| CMMOI  | M    | IILLIMETE | ER .  |

|--------|------|-----------|-------|

| SYMBOL | MIN  | NOM       | MAX   |

| A      | _    | _         | 1.77  |

| A1     | 0.08 | 0.18      | 0.28  |

| A2     | 1.20 | 1.40      | 1.60  |

| А3     | 0.55 | 0.65      | 0.75  |

| b      | 0.39 | -         | 0.48  |

| b1     | 0.38 | 0.41      | 0.43  |

| С      | 0.21 | _         | 0.26  |

| c1     | 0.19 | 0.20      | 0.21  |

| D      | 4.70 | 4.90      | 5. 10 |

| Е      | 5.80 | 6.00      | 6.20  |

| E1     | 3.70 | 3. 90     | 4.10  |

| е      |      | 1.27BSC   |       |

| L      | 0.50 | 0.65      | 0.80  |

| L1     |      | 1.05BSC   |       |

| θ      | 0    | _         | 8°    |

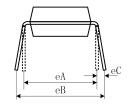

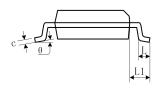

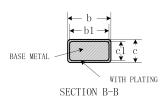

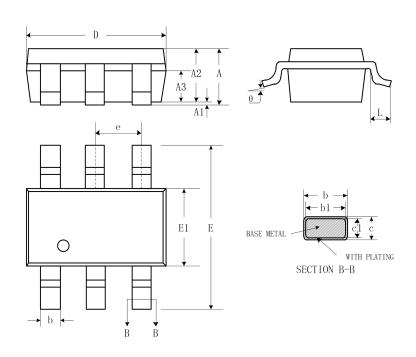

# 6.2 6PIN 封装尺寸

### 封装规格:

| Symbol | mm       |       |       | Inch      |       |        |

|--------|----------|-------|-------|-----------|-------|--------|

|        | MIN      | NOM   | MAX   | MIN       | NOR   | MAX    |

| A      | _        | _     | 1.35  | _         | _     | 0.053  |

| A1     | 0.04     | _     | 0. 15 | 0.002     | _     | 0.006  |

| A2     | 1.00     | 1.10  | 1.20  | 0.039     | 0.043 | 0.047  |

| A3     | 0.55     | 0.65  | 0.75  | 0.022     | 0.026 | 0.030  |

| b      | 0.30     | _     | 0.50  | 0.013     | _     | 0.017  |

| b1     | 0.30     | 0.40  | 0. 45 | 0.013     | 0.016 | 0.018  |

| С      | 0.08     | _     | 0. 22 | 0.006     | _     | 0.008  |

| c1     | 0.08     | 0.13  | 0. 20 | 0.003     | 0.005 | 0.08   |

| D      | 2.72     | 2. 92 | 3. 12 | 0.107     | 0.115 | 0. 123 |

| Е      | 2.60     | 2.80  | 3.00  | 0.102     | 0.110 | 0.118  |

| E1     | 1.40     | 1.60  | 1.80  | 0.055     | 0.063 | 0.071  |

| е      | 0. 95BSC |       |       | 0. 037BSC |       |        |

| L      | 0.30     | _     | 0.60  | 0.012     | _     | 0.024  |

| θ      | 0        | _     | 8°    | 0         | _     | 8°     |